5.2 时钟结构

上一章阐述了发送部分所有的模块,本章就开始对实现高速串行数据发送所需的模块进行详细的阐述。本章主要描述的有两个模块,一是数据接口,二是8B/10B编码。对于8B/10B编码的实现机制可参考我另一篇文章

第一步,我们先大致了解下用户接口是怎么配置的。

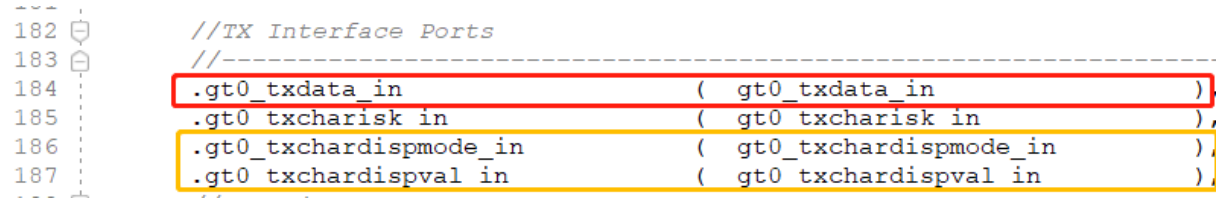

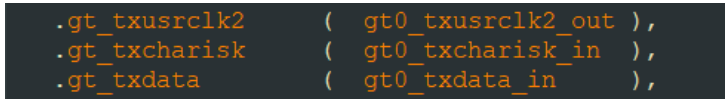

如下图是我们用户接口中涉及到的数据发送相关信号,看到这些信号,我想你会有这样三个疑问,一是这些信号都是干嘛的?如何实现数据发送呢?为啥会有两个时钟呢?接下来就对此一一解答。

首先,第一个问题,这些信号都是干嘛的?如下表所示

端口 | 方向 | 时钟域 | 描述 |

TXCHARDISPMODE [3:0] | In | TXUSRCLK2 | 这两个信号是搭配使用的 当禁用8B / 10B编码时: 用于扩展20位和40位TX接口的数据总线。 当启用8B / 10B编码时 用于手动实现运行差异(RD)的控制 |

TXCHARDISPVAL [3:0] | In | TXUSRCLK2 | |

TXDATA [31:0] | In | TXUSRCLK2 | 用于传输数据的总线。此端口的宽度取决于TX_DATA_WIDTH 若TX_DATA_WIDTH = 16,20:则TXDATA [15:0] = 16 当位宽是20或40时,则禁用8B / 10B编码器, TXCHARDISPVAL和TXCHARDISPMODE端口与TXDATA端口连接。 |

TXUSRCLK | In | Clock | 该端口用于为内部TX PCS数据路径提供时钟。 |

TXUSRCLK2 | In | Clokc | 该端口用于将FPGA逻辑与TX接口同步。当用户提供TXUSRCLK时,该时钟必须与TXUSRCLK正边沿对齐。 |

接下来我们来做进一步的阐述,以此了解如何实现数据发送的

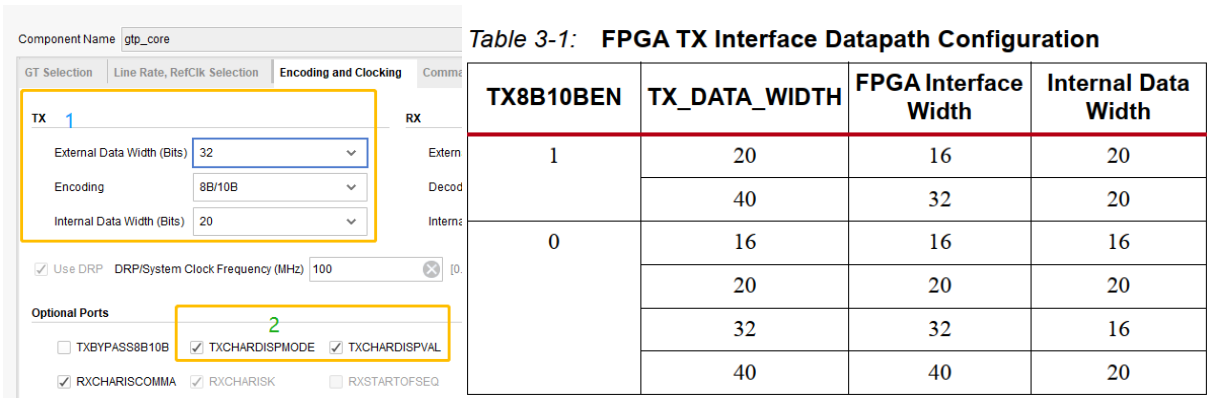

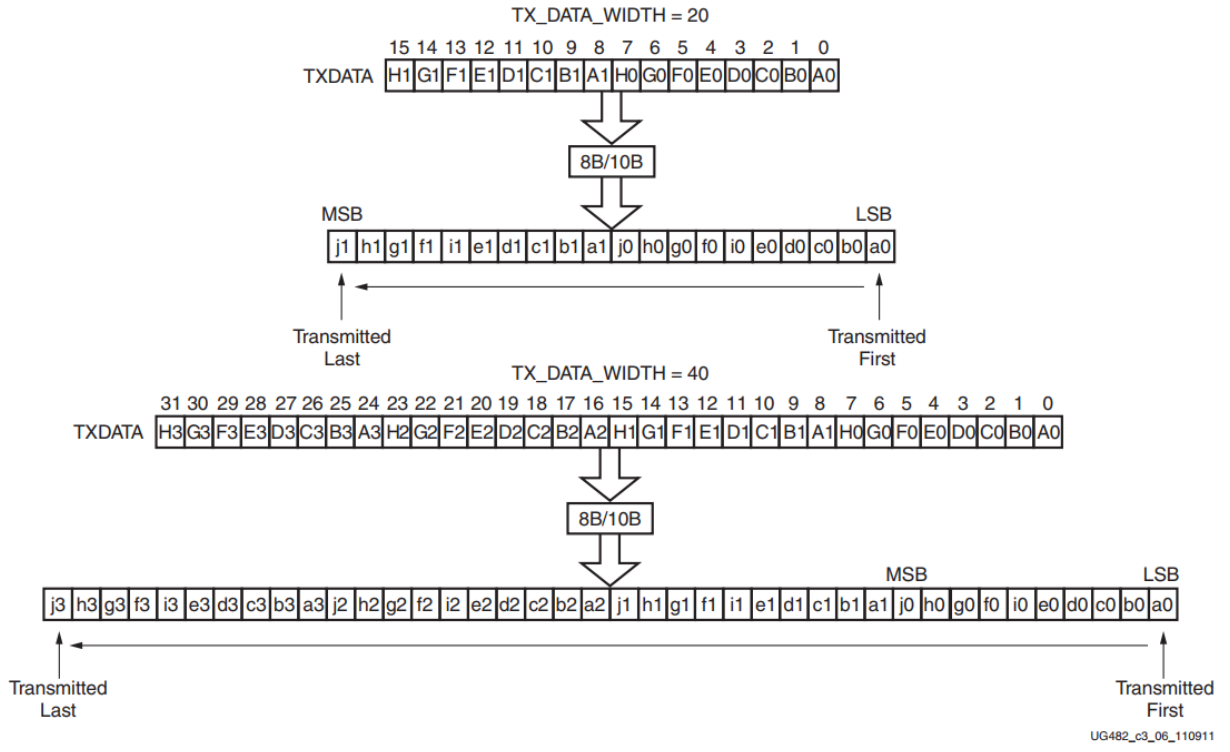

对于发送端的数据接口,我们有4种选择,也就是上表中的16、20、32、40。这在我们配置选项卡里可以通过配置实现,如下表。另外内部数据位宽“Internal Data Wudth(bits)”只有16和20两种选择,也就是说如果用户端选择了32或40,在其内部会进行一次转换。

对于8B/10B编码,我们可以使能也可以不使能也可以选择64B/66B编码。

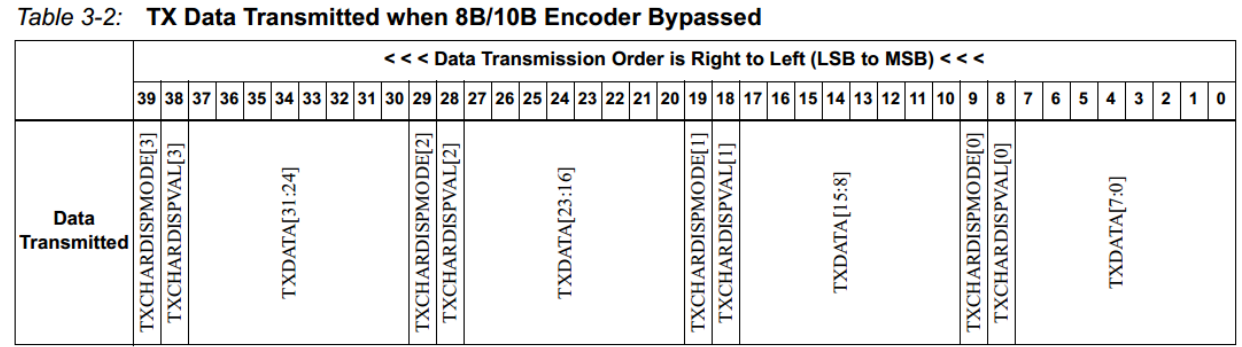

如果不使能的话,如上表所说,当我们数据接口在IP中配置为20或40时就需要“TXCHARDISPMODE”和“TXCHARDISPVAL”的帮忙了,如下表所示,我们可以定义一个20bit或40bit的寄存器,在赋值时按照下图分别赋值。

我们一般情况下是使能的,这样使用起来更简单,这时“TXCHARDISPMODE”和“TXCHARDISPVAL”就有了极性控制的作用。高速串行接口需要保证直流平衡,需要计算不平衡度,这是硬核模块会帮我们实现的,但我们也可以自己来控制,你看,不是说接口复杂呢?什么都可以让你看操作。如果自己控制就需要这两个信号了

TXCHARDISPMODE | TXCHARDISPVAL | 作用 |

0 | 0 | 这俩信号没用,有8B/10B硬核自动计算“RD” |

0 | 1 | 翻转运行差异 |

1 | 0 | 强制RD为负 |

1 | 1 | 强制RD为正 |

再插一句,如果上面有什么概念不懂,可参考《1.5 深入探究下高速串行通信常用的编码方式—8B/10B编码 (fpgaup.com)》一文,看来就懂了,如下是GTP的8B/10B编码方式,大概看看就行,而且ug482的附录C有具体的编码表。

再来说下最后一个问题,为什么俩时钟,这俩时钟干嘛的?具体的呢会在发送端口的时钟接口这章节描述,在这只需要知道,

如果用户数据接口是16或20bit,那么,TXUSRCLk2 = TXUSRCLK的,如果户数据接口是32或40bit,2TXUSRCLk2 = TXUSRCLK,就这么点关系,TXUSRCLK可以说没啥用

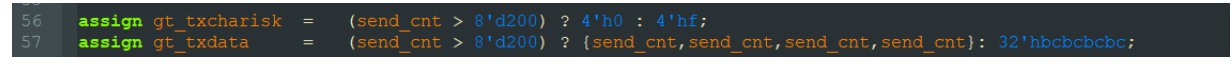

最后总结下,如果我们使能8B/10B编码且自己不控制不平衡度的话,那么数据发送接口只需要3个信号,如下图,另外那两或者在配置IP时不勾选,或者直接写0即可。

而且实现起来也很简单,将gt0_rxcharisk_out置一表示发送K码,否则就是发送数据

最后不得不说,GTP就是个纸老虎,看着那么多接口让人头疼,其实是为了实现其灵活性,真正的使用起来却是简单得很,所以不要畏难,那是你的双眼被蒙蔽了。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我