5.1 发送模块整体的介绍

本章就要开始介绍“GTPE2_CHANNEL”这个硬核或者说是原语内容了。本章的主要内容是对“GTPE2_CHANNEL”内部发送部分的框架进行大致的阐述,了解内部有什么东西,明白数据是怎么从用户接口发送出去的。

当我们要发送一包数据的时候,在用户接口实际用到的信号其中就是这个三个,一个时钟,一个类似数据有效信号、一个数据。我们把他写入到“GTPE2_CHANNEL”,该硬核就会将其按照你所配置的方式,转为串行数据发出。

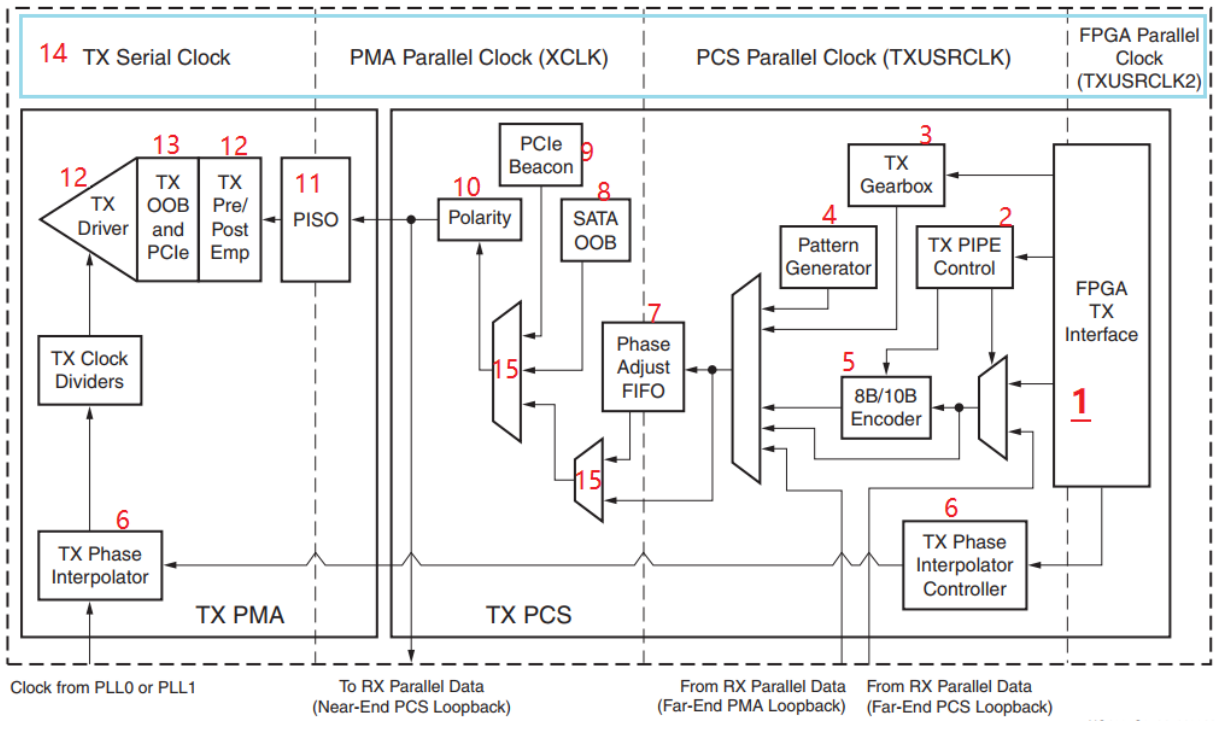

由于GTP的灵活特点和高速要求,所以“GTPE2_CHANNEL”内部包含了非常多的东西,如下图所示,我们可以将其分为两个部分,即PCS和PMA。

PCS(Physical Coding Sublayer)意思是物理编码子层,这不是xilinx自定义的一个名词,是具有普遍意义的,就是表示用户数据到串行数据间的处理过程,包括8B/10B编码、弹性缓冲区等等。

PMA(Physical Media Attachment)物理媒介适配层:这一层主要是接收PSC处理后的数据进行串并转换、预加重等功能。

但下图这些模块并不是都会用到,例如PCIE和SATA如果不做相关设计是必然不会用到的,所以,在本章会对每个模块进行大致的介绍,了解其功能,接下来章节会对用到的模块进行详细阐述,而这些模块也是我们实现高速串行接口的核心。

1、 FPGA TX Interface

就是用户数据的输入接口,也就是上述的

2、 TX PIPE Control

PIPE的全称是Physical Interface for PCI Express,即PCIe物理层接口,如果使能了PCIE接口,则该通道是PCIE的数据通道。

3、 TX Gearbox

GTP除了支持8B / 10B编码外还支持64B / 66B和64B / 67B编码方式,以此来提高有效数据的传输效率,支持这些通过对该模块的配置实现。

4、 Pattern Generator

伪随机序列(Pseudo-random bit sequences,PRBS)是一种貌似随机,实际上是有规律的周期性二进制序列,用于高速串行通信通道传输的误码率测试。

5、 8B/10B Encoder

8B/10B 编码是非常重要的一个知识点。位宽8bit可以组织出 256种数据,位宽10bit可以组织出1024种数据,我们就从这1024种数据中挑出一些0和1的个数应尽量相等的数据来表示8bit数据,另外还可以再挑出12种控制字符,来表示链路的状态或者控制信息,这不仅可以保持良好的直流平衡,增加了数据的传输距离,提供了更为有效的错误检测机制,还可以用来实现时钟修正、块同步、通道绑定和将带宽划分到子信道等

6、 TX Phase Interpolator Controller

这是TX相位插值器控制器模块,支持动态控制TX相位插值器(TX PI),TX PMA中的数据进行微调。

7、 Phase Adjust FIFO

为了保证数据传输速率一致,XCLK必须和TXUSERCLK时钟的速率匹配,并且要解决2个时钟域之间的相位差异。利用TX BUFFER介于XCLK和TXUSERCLK俩时钟域之间,用于匹配两者的速率和相位偏差。

8、 SATA OOB

SATA的全称是Serial Advanced Technology Attachment,即串口硬盘。OOB带外数据(Out of Band)。SATA的通讯建立主要是靠OOB(Out Of Band)的检测实现的,并且向上层Link Layer提供了物理层的连接情况。

9、 PCIE Beacon

提供PCIE的唤醒功能,由于不作为PCIE物理层接口,所以也是用不到

10、Polarity

这个很好理解嘛,就是对从PSC子层输出的编码数据,在发送端的串行化处理之前进行极性翻转。极性翻转只须将TXPOLARITY接口信号置位“1”即可。为啥要设置这个功能呢?为了兼容不同板卡间极性的不同或是PCB搞错的了情况。这也是个可选端口

11、PISO

PISO的全称是parallel input Serial output即并行输入串行输出,实现数据的串并转换功能

12、TX Configurable Driver

这包括“TX Pre/Post Emp”和“TX Driver”

其中TX Pre/Post Emp 的全称是Pre-cursor and post-cursor transmit pre-emphasis

GTP收发器TX驱动器是高速电流模式差分输出缓冲器。为了最大化信号完整性,它具有差分电压控制、前光标和后光标发送预加重、校准终端电阻功能,我们可以通过参数对其进行配置。如下为示意图,但还是默认吧,不要刚接触不要添乱了。

13、TX OOB and PCIE

这个主要是当GTP作为PCIE或SATA接口时所需要的功能, 忽略。

14、CLK

这又是重点,我们可以看到从用户接口的数据输入到串行数据的输出要跨四个时钟域,为什么要跨这么多时钟域呢?又是如何实现的呢?这将会以单独章节进行描述。

15、MUX

多路选择器,没什么好说的。

以上,即为GTP发送部分的所有模块,从分析来看,这部分不仅是实现串行数据的发出,同时也兼容了CPIE、SATA等接口,作为它们的物理层。但本系列视频着重介绍自定义协议的数据发出,也就是单纯的去了解咱们实现串行高速数据传输的,所以这些就不再阐述,而接下来着重要将的就是如下链路所涉及的内容。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我