2.2 GTP的硬核长什么模样?

第二部分:GTP的硬核长什么模样?

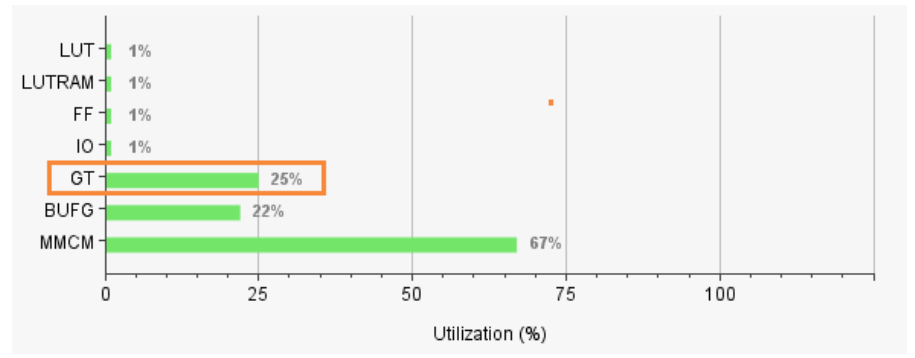

第一部分有用没用的扯了一堆,接下来就说一下GTP的硬核。一般我们把IP核分为软核、固核和硬核,硬核可以说嵌入在FPGA内部的ASIC,我们对他的使用是不占用查找表、触发器等逻辑资源的,而且有专门的资源统计,如下图所示,我用的芯片是ZYNQ系列的7015,一共有4个GT,就是四路串行高速接口,这我用了一个,故资源占用25%。

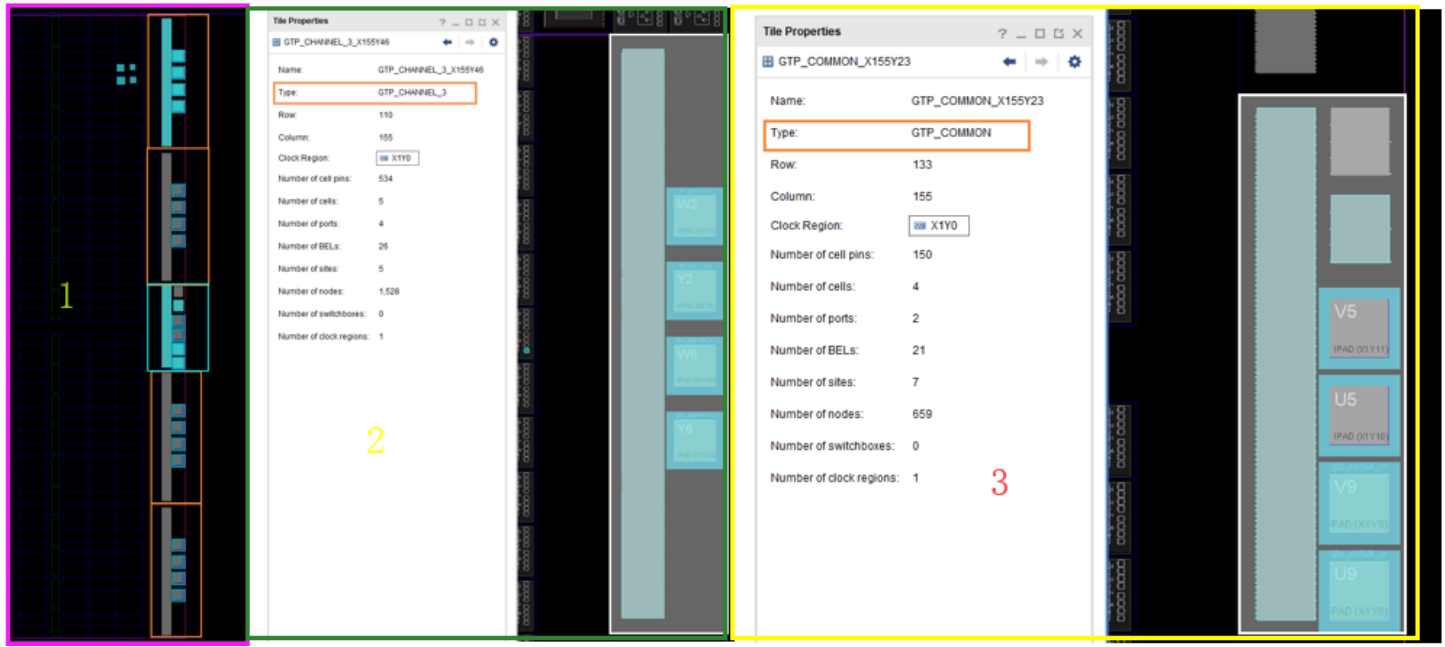

当然,硬核不占用其它资源不代表GTP这个IP核不占用其它资源,芯片厂家会对这个硬核封装,封装是耗费资源的。如下图所示,其中左1是一个整体,包括了4个名为左2的“GTPE2_CHANNEL”,右1是左1图中间的那部分,叫做“GTPE2_COMMON”。

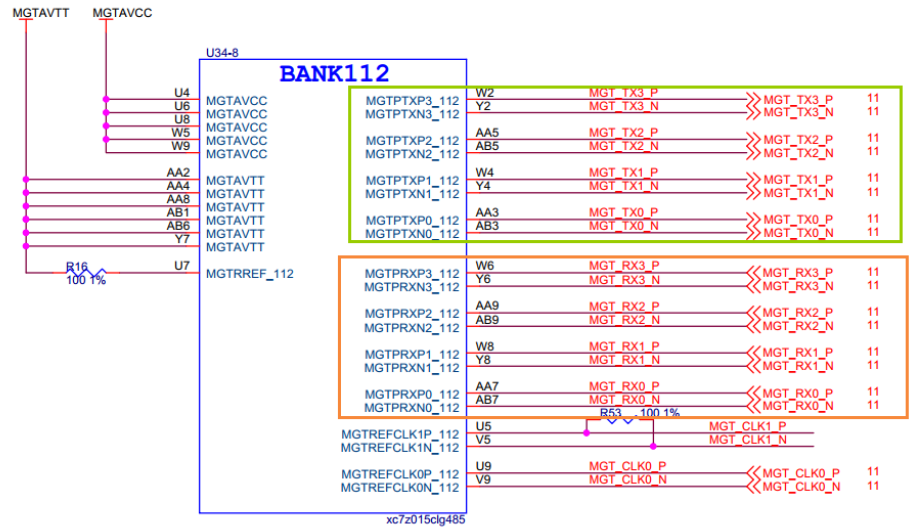

我们再放大看引脚可以发现,那四个“GTPE2_CHANNEL”是高速串行收发引脚,“GTPE2_COMMON”两组时钟,称之为“QPLL”,这就是xilinx的GTP硬核的组织形式,我们把这一组称之为一个“Quad” ,这在我们画原理图时也会有所体现。

但这样做的目的是什么呢?我认为这样做的目的是“好聚好散”,极大的提高应用的灵活性,对于PCIE、SRIO等协议,可能就是多通道,这样实现起来就更方便更灵活,因为我们不是说用四个就需要例化四个这样的IP核,他们是当做一组形成一个IP核。接下来看IP核的程序结构就可以发现这个现象。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我