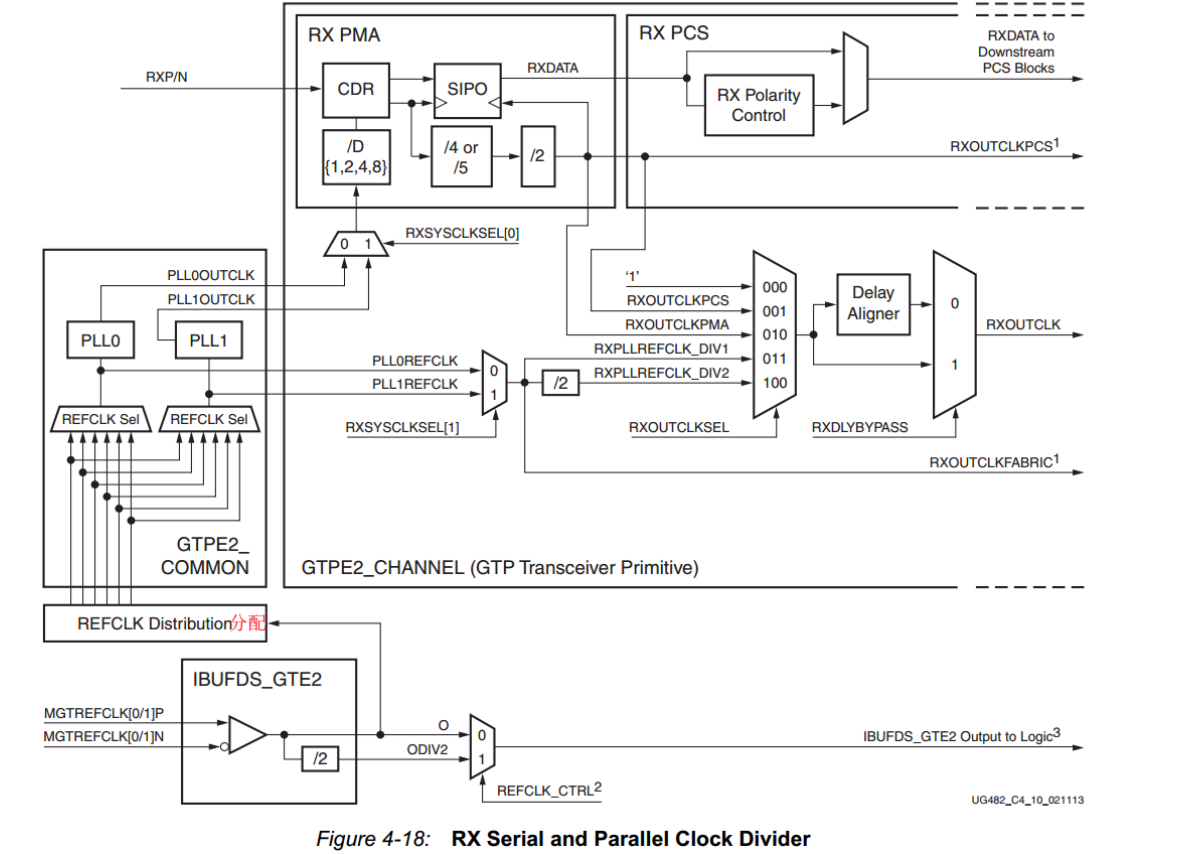

6.5 RX时钟输出结构

RX时钟分频器控制模块有两个主要组件:串行时钟分频器控制和并行时钟分频器和选择器控制。时钟分频器和选择器的详细信息如下图所示。其中需要注意的几点如下:

1、RXOUTCLKPCS和RXOUTCLKFABRIC是冗余输出。新设计是用RXOUTCLK

2、REFCLK_CTRL选项由软件自动控制,用户无法选择。用户只能将IBUFDS_GTE2的O或ODIV2输出之一路由到FPGA逻辑。

3、IBUFDS_GTE2是一个冗余输出,用于提供额外的时钟方案灵活性。

4.、选择/ 4或/ 5分频器块由GTPE2_CHANNEL原语的RX_DATA_WIDTH属性控制。

当RX_DATA_WIDTH = 20或40时选择/ 5,RX_DATA_WIDTH = 16或32.时选择/ 4。

每个发送器PMA模块都有一个D分频器,它将PLL的时钟分频,以降低线路速率。此串行时钟分频器D可以为具有固定线路速率的应用静态设置,也可以针对具有多个线路速率的协议动态更改。表4-16中描述了串行分频器的控制。有关每个速度等级的线速范围的详细信息,请参见相应数据手册的7系列FPGA文档页面。

要在固定线路速率应用中使用D分频器,必须将RXOUT_DIV属性设置为适当的值,并且RXRATE端口需要连接到3'b000。有关详细信息,请参阅表4-16中的“通过属性进行静态设置”列。

要在多个线路速率应用中使用D分频器,RXRATE端口用于动态选择D分频器值。RXOUT_DIV属性和RXRATE端口必须在器件配置时选择相同的D分频器值。设备配置后,RXRATE用于动态更改D分频器值。有关详细信息,请参阅表4-16中的“通过端口动态控制”一栏。

我们可以选择时钟的路径。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我