6.15 Rx 接口

FPGA RX接口是FPGA通往GTP收发器的RX数据通路的网关。

应用程序通过从RXUSRCLK2上升沿的RXDATA端口读取数据,通过GTP收发器接收数据。端口的宽度可以配置为两个或四个字节宽。端口的实际宽度取决于RX_DATA_WIDTH属性和RX8B10BEN端口设置。端口宽度可以是16,20,32和40位。接口处的并行时钟(RXUSRCLK2)的速率由RX线路速率,RXDATA端口的宽度以及是否启用8B / 10B解码确定。在某些工作模式下,必须为发送器中的内部PCS逻辑提供第二个并行时钟(RXUSRCLK)。本节介绍如何驱动并行时钟并解释这些时钟对正确操作的限制。

7系列GTP收发器包含一个2字节的内部数据通路。

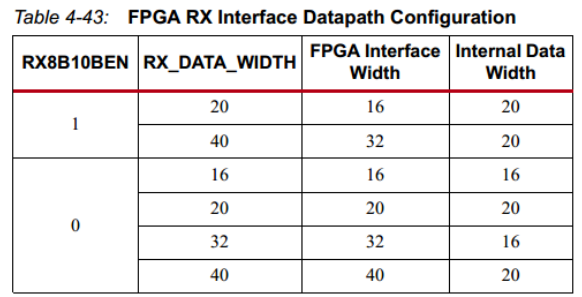

可通过设置RX_DATA_WIDTH属性来配置FPGA接口宽度。

当使能8B / 10B解码器时,RX_DATA_WIDTH必须配置为20位或40位,在这种情况下,FPGA RX接口仅使用RXDATA端口。

例如,当FPGA接口宽度为16时使用RXDATA [15:0]。当绕过8B / 10B解码器时,RX_DATA_WIDTH可配置为任何可用宽度:16,20,32或40位。

表4-43显示了如何选择RX数据路径的接口宽度。

在RX 8B / 10B解码器,第170页中更详细地描述了8B / 10B解码。

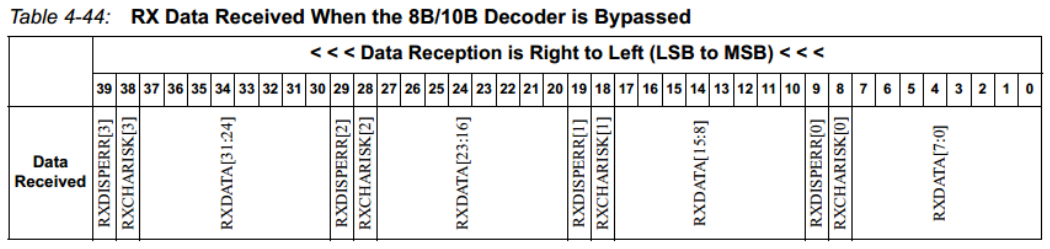

当8B / 10B解码器被旁路且RX_DATA_WIDTH为20或40时,RXDISPERR和RXCHARISK端口用于将RXDATA端口从16位扩展到20位,或32到40位。

表4-44显示了禁用8B / 10B解码器时收到的数据。使用RX变速箱时,请参阅RX变速箱,页面207了解数据传输顺序。

RXUSRCLK和RXUSRCLK2的生成

FPGA RX接口包括两个并行时钟:RXUSRCLK和RXUSRCLK2。

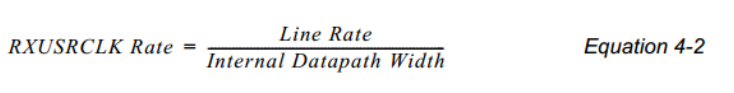

RXUSRCLK是GTP收发器发送器中PCS逻辑的内部时钟。RXUSRCLK所需的速率取决于GTPE2_CHANNEL原语的内部数据路径宽度和GTP收发器发送器的RX线路速率。公式4-2显示了如何计算RXUSRCLK所需的速率。

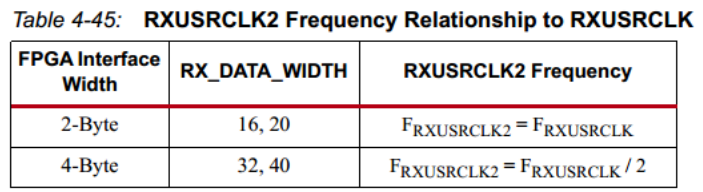

RXUSRCLK2是进入GTP收发器RX侧的所有信号的主同步时钟。进入GTP收发器RX端的大多数信号在RXUSRCLK2的上升沿采样。RXUSRCLK2和RXUSRCLK具有基于RX_DATA_WIDTH设置的固定速率关系。表4-45显示了每RX_DATA_WIDTH值的RXUSRCLK2和RXUSRCLK之间的关系。

对于RXUSRCLK和RXUSRCLK2,必须遵守这些关于时钟之间关系的规则:

l RXUSRCLK和RXUSRCLK2必须是正边沿对齐的,它们之间的偏差尽可能小。因此,应使用低偏移时钟资源(BUFG和BUFH)来驱动RXUSRCLK和RXUSRCLK2。

l 如果通道配置为相同的振荡器驱动发送器和接收器的参考时钟,则TXOUTCLK可用于驱动RXUSRCLK和RXUSRCLK2,其方式与驱动TXUSRCLK和TXUSRCLK2的方式相同。当时钟校正关闭或RX缓冲器被旁路时,必须使用RX相位对齐来对齐串行时钟和并行时钟。

l 如果单独的振荡器驱动通道上的发送器和接收器的参考时钟,并且不使用时钟校正,则RXUSRCLK和RXUSRCLK2必须由RXOUTCLK驱动(RXOUTCLKSEL = 3'b010用于RXOUTCLKPMA),并且相位对齐电路必须是用过的。

l 如果使用时钟校正,RXUSRCLK和RXUSRCLK2可以由RXOUTCLK或TXOUTCLK提供。

端口和属性

端口 | 方向 | 时钟域 | 描述 |

RXDISPERR [3:0] | Out | RXUSRCLK2 | 禁用8B / 10B解码时,RXDISPERR用于扩展20位和40位RX接口的数据总线. 高电平有效表示RXDATA上显示的相应字节有差异错误。 RXDISPERR [3]对应RXDATA [31:24] RXDISPERR [2]对应RXDATA [23:16] RXDISPERR [1]对应RXDATA [15:8] RXDISPERR [0]对应RXDATA [7:0] |

RXCHARISK [3:0] | Out | RXUSRCLK2 | 禁用8B / 10B解码时,RXCHARISK用于扩展20位和40位RX接口的数据总线。 高电平有效表示当启用8B / 10B解码时,RXDATA上显示的相应字节为K字符。 RXCHARISK [3]对应RXDATA [31:24] RXCHARISK [2]对应RXDATA [23:16] RXCHARISK [1]对应RXDATA [15:8] RXCHARISK [0]对应RXDATA [7:0] |

RXDATA [31:0] | Out | RXUSRCLK2 | 用于传输数据的总线。该端口的宽度取决于RX_DATA_WIDTH:RX_DATA_WIDTH = 16,20:RXDATA [15:0] = 16位宽RX_DATA_WIDTH = 32,40:RXDATA [31:0] = 32位宽当20位或40位时需要总线,8B / 10B编码器的RXCHARISK和RXDISPERR端口与RXDATA端口连接。请参见表4-44,第214页。 |

RXUSRCLK | In | Clock | 该端口用于为内部RX PCS数据路径提供时钟 |

RXUSRCLK2 | In | Clock | 该端口用于将FPGA逻辑与RX接口同步。当用户提供RXUSRCLK时,该时钟必须与RXUSRCLK正边沿对齐。 |

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我