3.3 GTP的时钟结构分析(下)

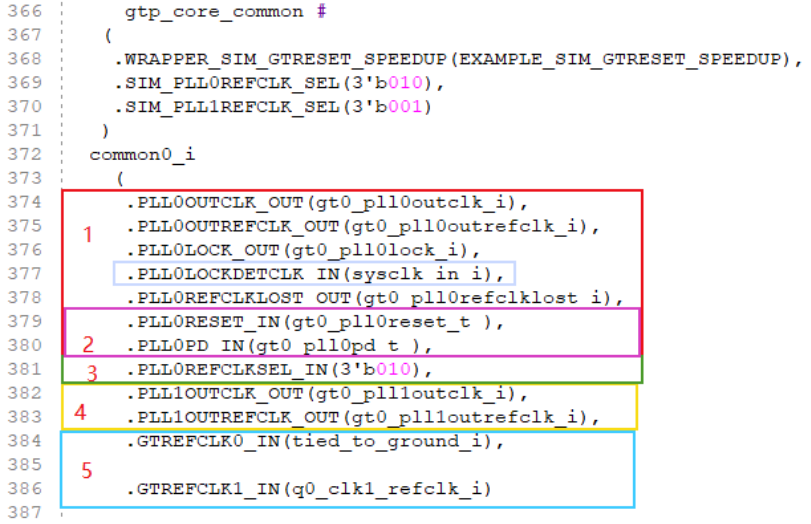

对核内部就不去做过多的分析了,没有必要,而且我也说不清。我们看下对外接口信号。我们大致的把输入信号分为五个部分,我们倒着看,下面对此进行依次解释。

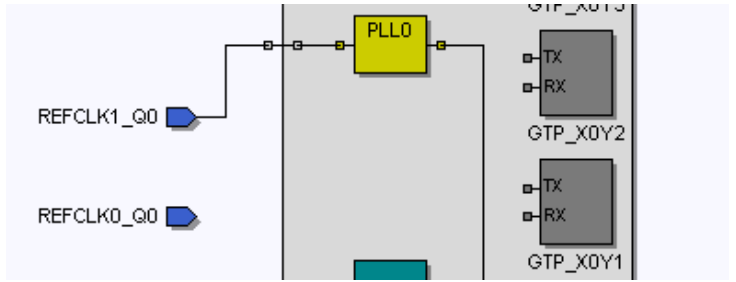

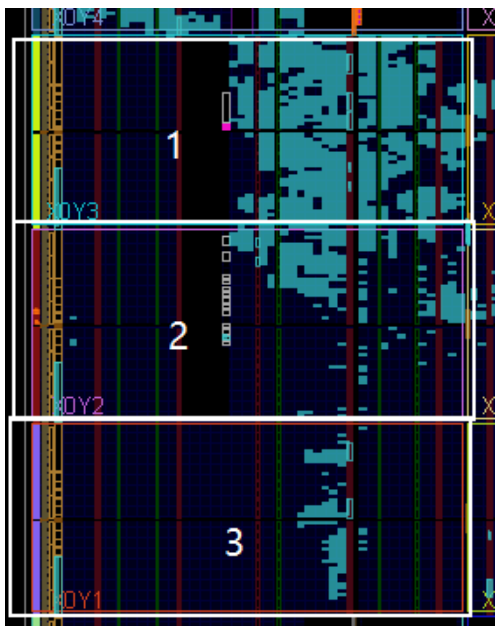

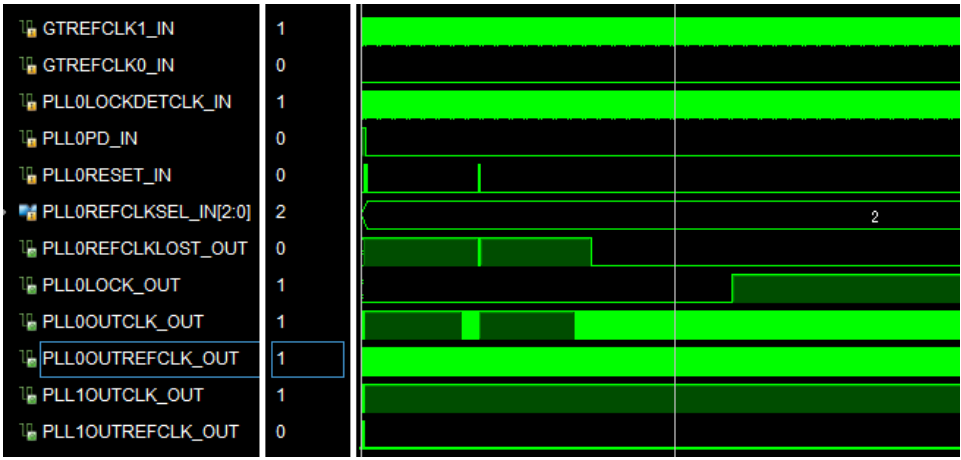

(5)是高速串行接口的专用输入时钟转单端后接入的。我们看到有两个,CLK1和CLK0。这无论是和原理图还是IP核的配置都是吻合的,如下图是我的配置,之所以用REFCLK1_Q0是因为原理图已经设计好了。

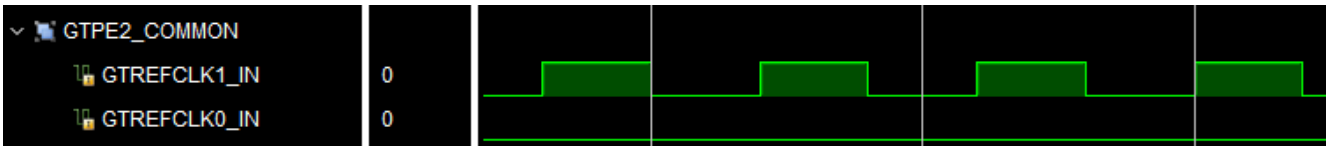

也正因此,可以看到“GTREFCLK0_IN”是没有时钟输入的

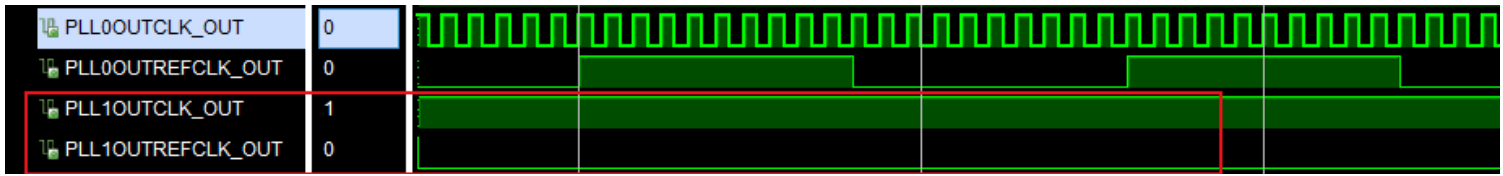

(4)这是给“GTPE2_CHANNEL”的时钟,一个是用于处理并行数据的时钟,一个是用于处理串行数据的时钟,具体这两个时钟是如何应用的,会在下面章节阐述。根据上图IP核的配置可以看出,我用的是PLL0,所以PLL0有相关的输出有时钟,PLL1的没有。

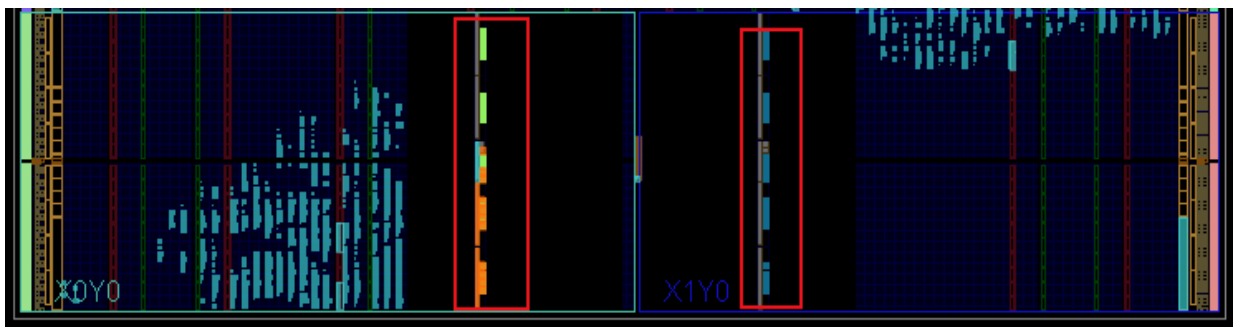

(3)“PLL0REFCLKSEL_IN”这个信号还是挺有讲头的,表示输入时钟的选择。这涉及到了GT系列的时钟架构,也是GTP和TGX的一大区别所在。这个GTP的输入时钟选择示意图,GTX与之有区别,在下文描述。这两组GTP分别来自X0Y0和X1Y0两个BANK。他们的时钟是可以共用的。

首先,红色部分是晶振输入时钟,每个Quad有两个选择,这个在已经说过多次了,随后这个两个时钟会经过上文所说的“IBUFDS_GTE2”转单时钟,随后会进行路由到相邻的BANK,这就是xilinx所说的“东西”路由,两个不同BANK的时钟可以共享如下图所示

这样PLL可以有四个时钟输入源可供选择了,但我们看实际上有七个时钟可供选择呢?那剩下三个呢? 其中一个是“GTGREFCLK*”,这个参考时钟由内部FPGA逻辑生成,此输入仅供内部测试之用。还有两个,是空下的,也就是GTP只能从5个里面选1个,这是由GTP结构决定的。空下那两个是给GTX用的,因为GTX不是“东西”路由,而是“南北路由”如下示意图,这样的三个BANK的高速串行接口时钟共享,这样就有7个时钟可供选择了(下图只是示意图,所以没有看到高速串行接口模块)

(2)这就是在“2”中描述的内容,也就是“gtp_core_cpll_railing”模块产生的复位信号,当然还有其它模块的复位,这个就不在重复叙述了

(1)这里面就是“GTPE2_COMMON”模块输出的时钟及状态。当然,还有一个碍事的“sysclk_in_i”,这个时钟是用于检测到PLL的反馈和参考时钟信号的。除此之外,PLL0OUTCLK_OUT、PLL0OUTREFCLK_OUT如上文,给“GTPE2_CHANNEL”的。“PLL0LOCK_OUT”是PLL锁定信号,“PLL0REFCLKLOST_OUT”是PLL失锁信号。以上即为本模块所有信号。

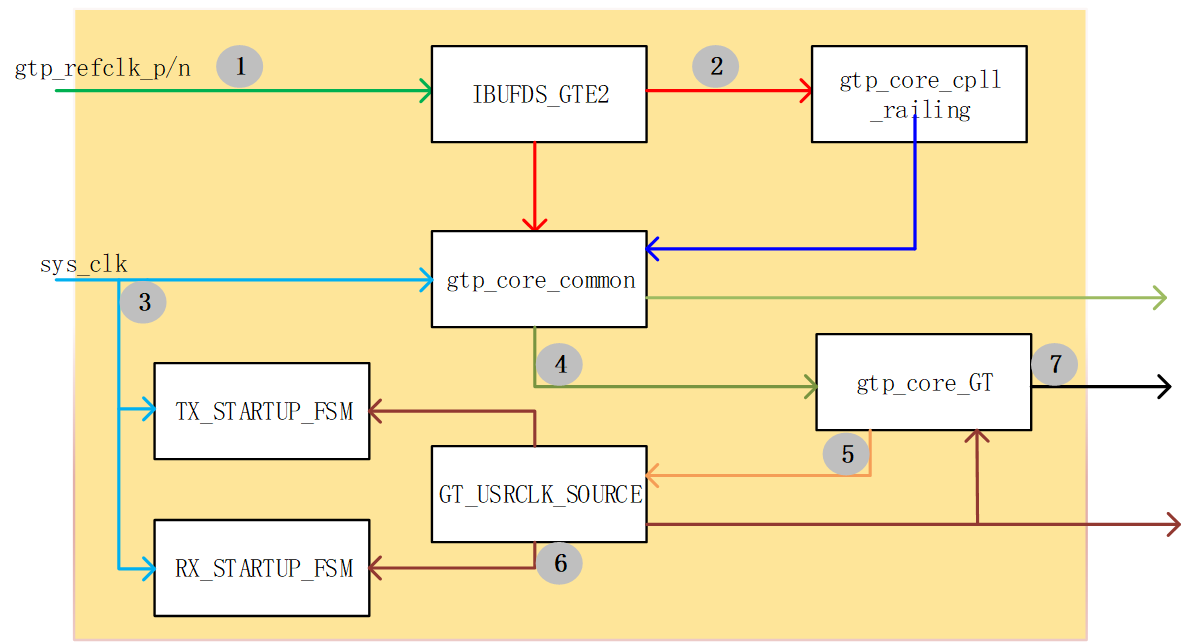

我们继续下面这个图的分析

5、6、7这三个是可以合起来说的。

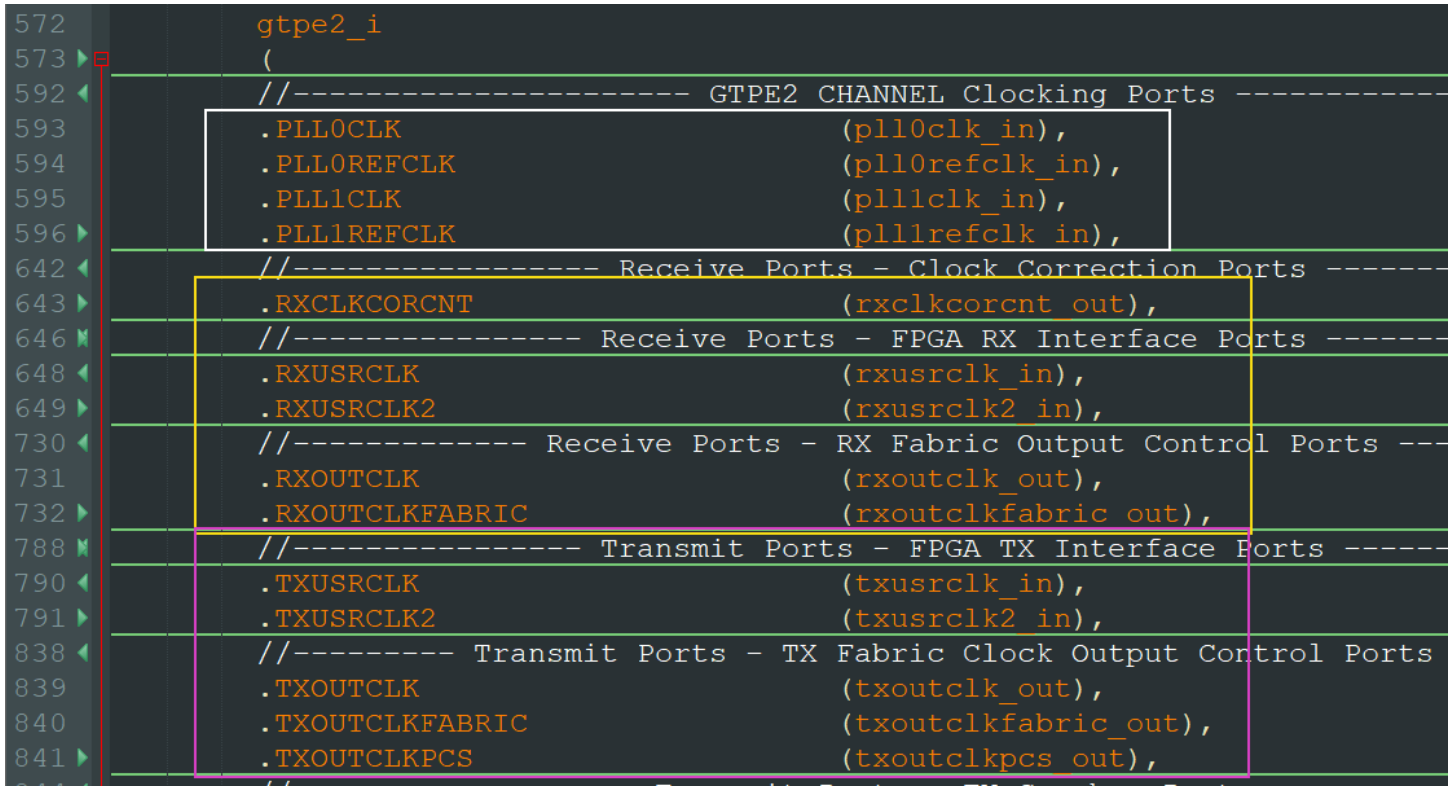

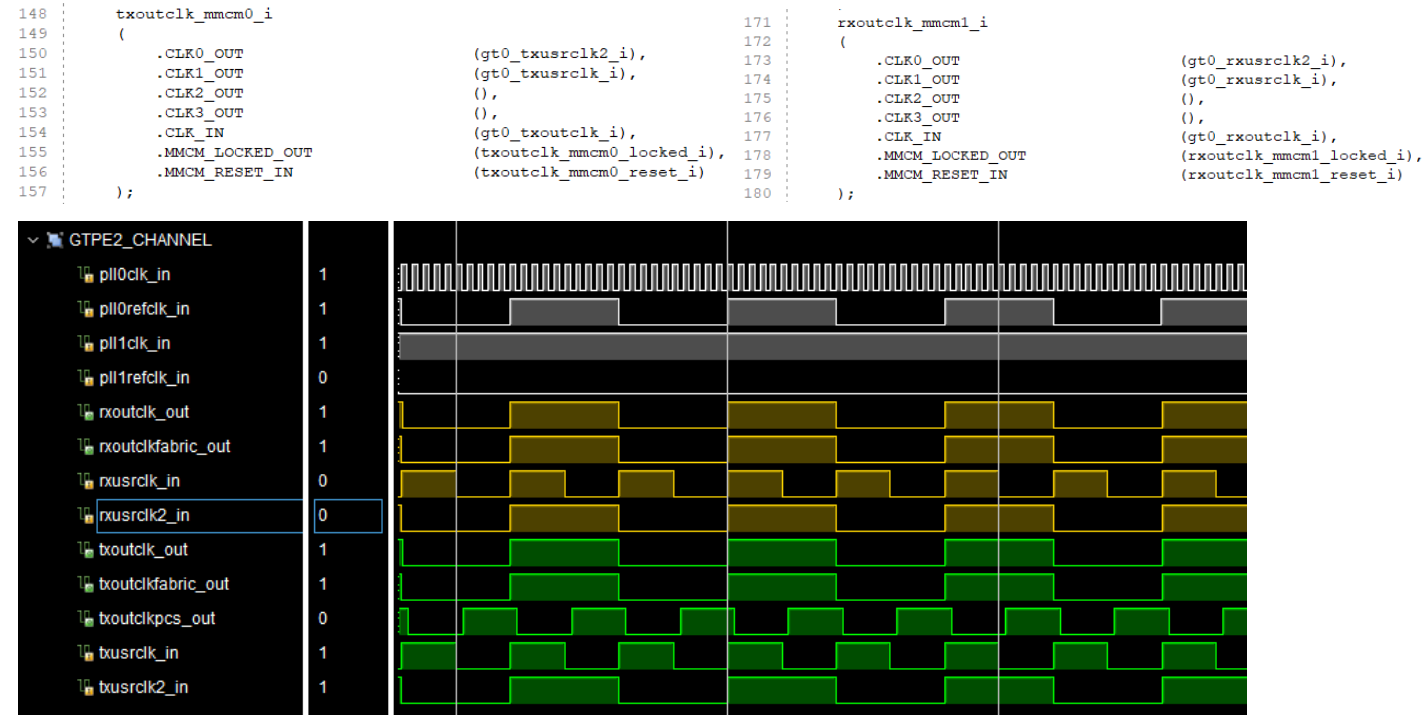

是“gtp_core_GT”模块的输出时钟,这个模块主要是对“GTPE2_CHANNEL”的封装,我们从如下图可以看到上文介绍的输入时钟、和输入与输出相关的时钟。

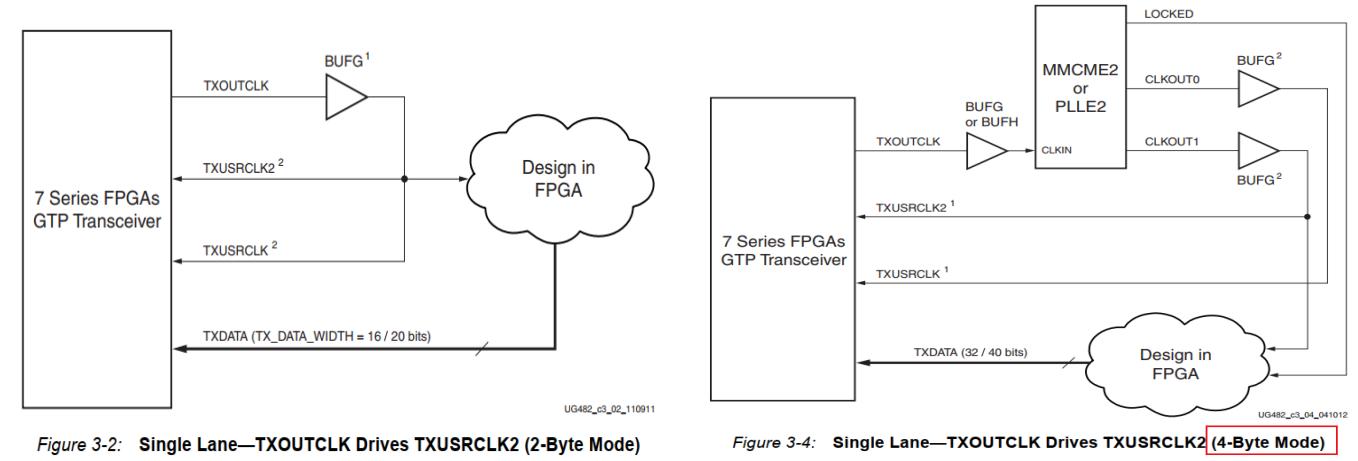

我们看RX和TX相关时钟很有特点哈,都是三个输出两个输入,其中那两个输入就是根据各自的输出得来的,在“gtp_core_GT_USRCLK_SOURCE”模块经过PLL,得到的。

如果选择外面数据接口为16bit则不需要这两个PLL,这一下子消耗两个PLL也着实有点浪费。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我