5.3 其他模块

下面在说下其他模块,这些模块不是很复杂而且有些也是不常用,就放一堆儿一块描述了。例如“TX OOB and PCIe”、“SATA OOB”等就不阐述了,目前我不会。

5.3.1 发送缓冲(跨时钟域)

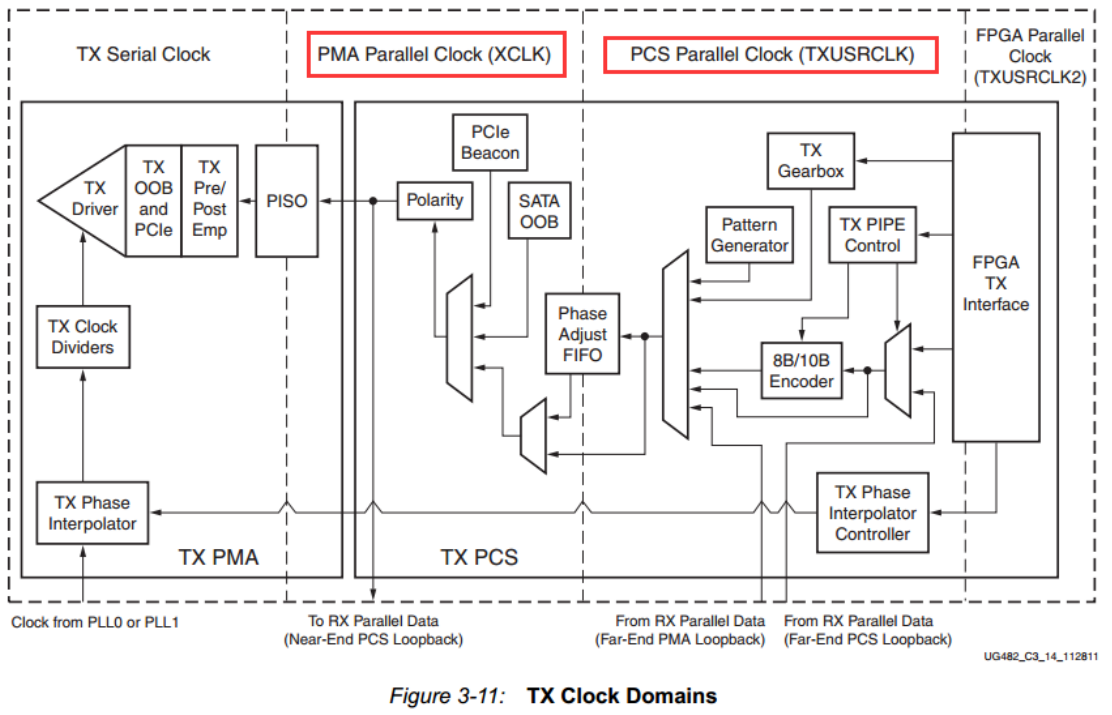

如下图是时钟域的划分,在发送端的PCS子层里面有两个并行时钟域,分别是PMA相连的并行时钟(XCLK)和TXUSRCLK时钟,如下图所示。为了保证数据传输速率一致,XCLK必须和TXUSERCLK时钟的速率匹配,并且要解决2个时钟域之间的相位差异。利用TX BUFFER介于XCLK和TXUSERCLK俩时钟域之间,用于匹配两者的速率和相位偏差。

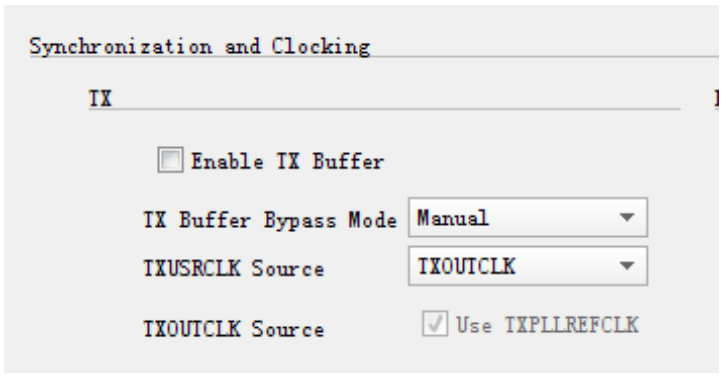

根据上图我们可以看出,这个TX BUFFER是可以旁路掉的,就是配置选项卡里面这个选项,如果不使能缓冲,可以采用相位对齐的方式,我们可以看到在不勾选“Enable TX Buffer”时候,可以选择时钟源和旁路模式,具体可以看ug482.

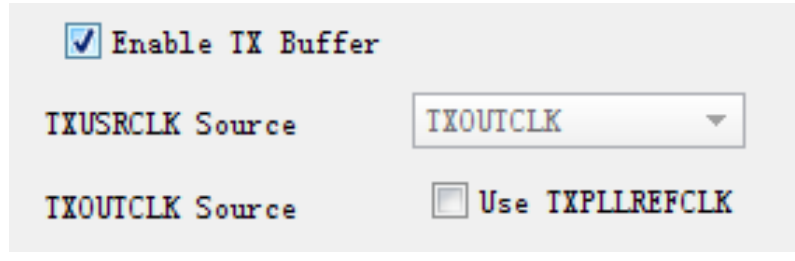

对于我等入门选手还是选择使能吧,界面如下还可以确定TXOUTCLK时钟源。建议打勾

此外,关于TX BUFFER还有一个表示状态的信号——TXBUFSTATUS,这是一个可选端口,具体含义如下表所示:

端口 | 方向 | 时钟域 | 描述 |

TXBUFSTATUS [1:0] | Out | TXUSRCLK2 | TX缓冲状态。 TXBUFSTATUS [1]:TX缓冲区溢出或下溢状态。当TXBUFSTATUS [1]设置为高电平时,它将保持高电平,直到TX缓冲区复位。 1:TX FIFO发生上溢或下溢。 0:无TX FIFO溢出或下溢错误。 TXBUFSTATUS [0]:TX缓冲区充满度。 1:TX FIFO至少半满。 0:TX FIFO小于半满。 |

只要TXBUFSTATUS指示上溢或下溢情况,就应复位TX缓冲区。当TXBUF_RESET_ON_RATE_CHANGE = TRUE时,可以使用GTTXRESET,TXPCSRESET或GTP收发器在内部生成的TX缓冲器复位速率变化来复位TX缓冲器。GTTXRESET的断言触发一个序列,该序列重置GTP收发器的整个发送器。

5.3.2 发送缓冲旁路模式

旁路TX BUFFER是7系列GTP收发器的高级功能。TX相位对准电路用于调整PISO并行时钟域和TX XCLK域之间的相位差,以将数据从PCS传输到PISO。它还通过连续调节TXUSRCLK来执行TX延迟校准,以补偿温度和电压变化。组合的TX相位和延迟对准必须由用户手动控制。具体描述在需要的时候再看吧。现在看了也记不住。

5.3.3 PRBS 伪随机序列码

伪随机序列(Pseudo-random bit sequences,PRBS)是一种貌似随机,实际上是有规律的周期性二进制序列,具有良好的随机性和接近于白噪声的相关函数。这些特性使得伪随机序广泛应用于误码率测量、演示测量、噪声发生器、通信加密和扩频通信等领域。在高速设计中为了测量高速串行通信通道传输的误码率,通常通过发送PRBS码来进行检测。

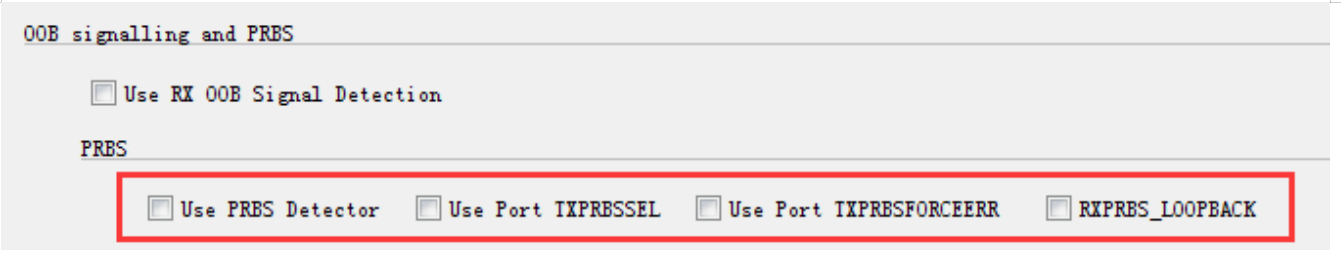

关于PRBS的随机特性。在PRBS码流中,二进制数“0”和“1”是随机出现的,但是它又和真正意义上的随机码不同,这种“随机”特性只是局部的,即在周期内容部,但各个周期中的码流却是完全相同的,所以称其为“伪随机码”。PRBS码的周期长度与其阶数有关,常用的阶数有7、9、11、15、20、23、31,也就是常说的PRBS7、PRBS9、……。这些配置是通过选项卡的这些端口实现的,如下图所示。事先配置好阶数,发送端编码,接收端解码,完成了校验。

5.3.4 发送端的极性控制

这个很好理解嘛,就是对从PSC子层输出的编码数据,在发送端的串行化处理之前进行极性翻转。极性翻转只须将TXPOLARITY接口信号置位“1”即可。为啥要设置这个功能呢?为了兼容不同板卡间极性的不同或是PCB搞错的了情况。这也是个可选端口

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我