7.3 Encoding and Optional Ports (编码和可选端口)

向导的第2页(图2-2)允许您选择收发器位置、时钟及数量。

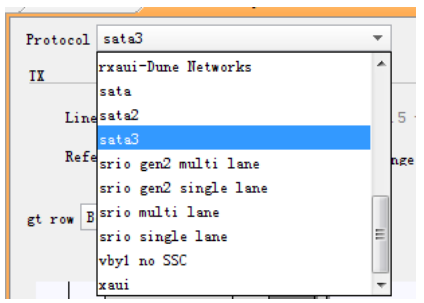

Protocol是选择协议,下拉菜单里面有各种各样的协议,在这里选择不同的协议只是为确定线速率及参考时钟提供便利,因为不同协议的速率是固定的,比如sata3是6Gbps,并不会产生其他的影响,从这也可以看出,依靠该核可以实现很多种协议。我们一般选择“start from scratch”,翻译为“白手起家”,我们可以理解为不构建任何协议,从最原始本初开始。

使用表4-7和表4-8确定线路速率和参考时钟设置。

选项 | 描述 |

Line Rate | 设置为Gb/s的所需目标线路速率。可以独立于接收线路速率。 |

Reference Clock | 从列表中选择应用程序提供的最佳参考时钟频率。 |

Txoff | 选择此选项可禁用收发器的TX路径。收发器仅用作接收器。 |

表4-8:RX设置

选项 | 描述 |

Line Rate | 设置为Gb/s的所需目标线路速率。可以独立于接收线路速率。 |

Reference Clock | 从列表中选择应用程序提供的最佳参考时钟频率。 |

Rxoff | 选择此选项可禁用收发器的RX路径。 |

使用表4-9到4-12确定此页面上提供的可选端口设置。

选项 | 描述 |

Use Common DRP | 选择此选项可使应用程序可以使用COMMON块的动态重配置端口信号 |

Advanced Clocking Option | 使用此复选框可将所有可能的参考时钟端口显示给生成的包装器。用于动态时钟切换。 |

PRBS pattern generator and check | PRBS模式产生和检测功能经常用来验证链路质量金额抖动容忍测试。 |

Vivado Design Suite Debug Feature | 使用此复选框可以显示IP中的ILA和VIO内核,以进行硬件调试和控制。有关使用硬件中的ILA和VIO内核进行调试的更多详细信息,请参阅KC705评估板上的7系列GT向导硬件验证,第127页。 |

表4-10:选择收发器和参考时钟

选项 | 描述 |

GT | 按位置选择要在目标设计中使用的各个收发器。 |

TX时钟源 | 确定提供给每个所选收发器的参考时钟信号的来源(参见表4-12)。每四个收发器提供两个差分时钟信号输入引脚,标记为REFCLK0和REFCLK1。这些组从收发器列的底部开始标记为Q0到Q4。每个收发器可以根据收发器位置访问本地信号组和一个或两个相邻组。 |

RX时钟源 |

表4-11:PLL选择、

选项 | 描述 |

QPLL | GTX和GTH收发器:当Quad的所有四个收发器用于节省功率时,使用Quad PLL。四路PLL在四路收发器之间共享。 |

CPLL | GTX和GTH收发器:根据所选收发器支持的线路速率使用通道PLL。 |

PLL0 | 仅限GTP收发器:PLL0在四个四通道收发器之间共享 |

PLL1 | 仅限GTP收发器:PLL1在四个四通道收发器之间共享。 |

REFCLK0/1Q0 | 收发器Y0-Y3的本地参考时钟 |

REFCLK0/1Q1 | 收发器Y4-Y7的本地参考时钟 |

REFCLK0/1Q2 | 收发器Y8-Y11的本地参考时钟 |

REFCLK0/1Q3 | 收发器Y12-Y15的本地参考时钟 |

REFCLK0/1Q4 | 收发器Y16-Y19的本地参考时钟 |

REFCLK0/1Q5 | 收发器Y20-Y23的本地参考时钟 |

REFCLK0/1Q6 | 收发器Y24-Y27的本地参考时钟 |

REFCLK0/1Q7 | 收发器Y28-Y31的本地参考时钟 |

REFCLK0/1Q8 | 收发器Y32-Y35的本地参考时钟 |

对于REFCLK0,CPLL / QPLL / PLL0 / PLL1REFCLKSEL始终连接到001,而REFCLK1则为010,无论时钟是来自北方还是南方四方。 如果您计划使用北极或南极四极管的参考时钟,则必须遵循更改参考时钟的指导原则,该指南可在设备的相应收发器用户指南中找到。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我