3.8 PCIE的RC、SW、EP有着怎样的结构

这是剖析PCIE协议的第18篇文章

内容简介

2024-01-30

PCIE是PCI的升级版,主要是物理实现方式的升级,其次是伴随物理链路升级而产生的实现方式的优化。例如配置空间的访问机制,不仅兼容PCI的配置空间访问机制,还提供了增强型的配置空间访问机制,例如配置空间,不仅兼容PCI的256Byte的配置空间,还扩展了4KB的配置空间。所以PCIE有着PCI的身影,但也有着自己的特点。

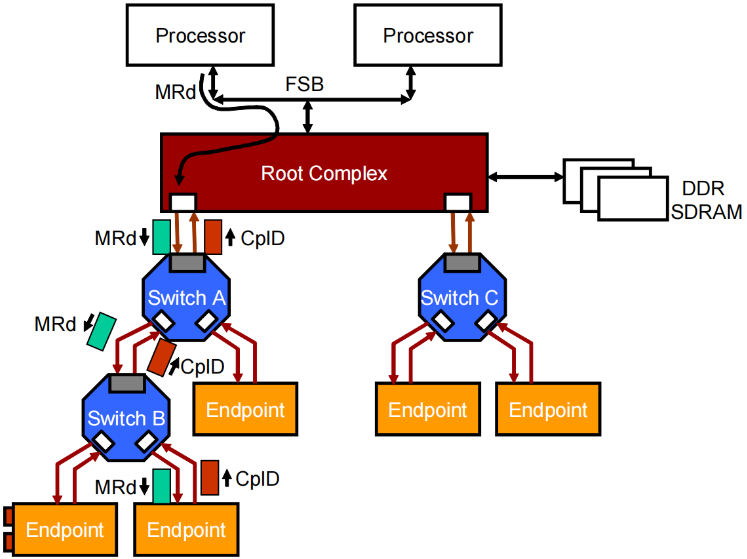

如下图是一个PCIE的拓扑结构图,包含了RC、switch和EP三大要素,下面我们分别从结构方面入手来介绍以下

Root Complex(RC)

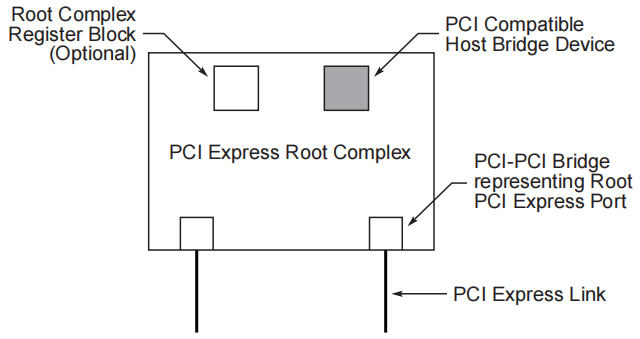

Root Complex简称RC,类似于PCI的host主桥,对于RC没有明确的规范要求,在不同的处理器中有着不同的实现方式,但总体上与PCI一样具备HOST主桥的功能。例如上图所示,处理器通过FSB链接到了RC。FSB是Front-Side Bus的缩写,是一种传统的系统总线,它连接了计算机的主要组件,如 CPU、内存和北桥芯片。上图的RC由一个存储器控制器和两个PCI桥组成,这个PCI桥链接着Switch。总的来说,RC是PCIE体系结构的一个重要组成部件,是PCIE树的根,是整个PCIE树的控制者。但这个部件具体是什么样子的,可以根据实际需求来定,但唯一可以确定的,必须包含PCIE的总控制器的功能,所以RC的总线编号为0,挂在RC下的设备总线编号也都是0,并依次向下延伸。

switch

switch的主要作用是扩展链路,在这里主要了解下switch内部的结构大致是什么样子的。如下图一个标准的switch具备一个上游端口和多个下游端口,上游端口可链接RC和switch,下游端口可以链接EP、switch以及不怎么用的PCI桥。而且switch还支持几个下游端口间的数据交互以及不同switch间的下游端口的数据交互,不过这些功能都是可选的。

PCIE是点对点的连接方式,这与PCI是有很大的不同,PCIE的一条链路只能链接一个设备。Switch内部是由多个PCI-PCI桥组成,每一个上游和下游端口都有对应的一个虚拟PCI桥,在一个switch中有多少个端口,在其内部就有多少个虚拟PCI桥,就有多少个PCI桥配置空间,而且配置空间的header类型一定是Type01。switch内部可以说具有一条虚拟的PCI总线,用于连接各个虚拟PCI桥,系统软件在初始化switch时,需要为这条虚拟PCI总线编号。

试想以下,switch作为一对多的传输通道,肯定会有数据冲突的情况,也就需要关注服务质量(QoS)的问题。PCIE总线采用多通道VC技术,并在这些数据报文中设定一个TC标签来确定优先级。具体的将在后续章节描述。

Endpoints

也就是PCIE设备,可连接到RC或switch上。这里与PCI有个区别,PCI的一条总线上可以有多个PCI设备。PCIE采用点对点的连接方式,所以每条总线上只有一个PCIE设备,例如上图switch的结构图,下游有两个端口,也就是两条总线。

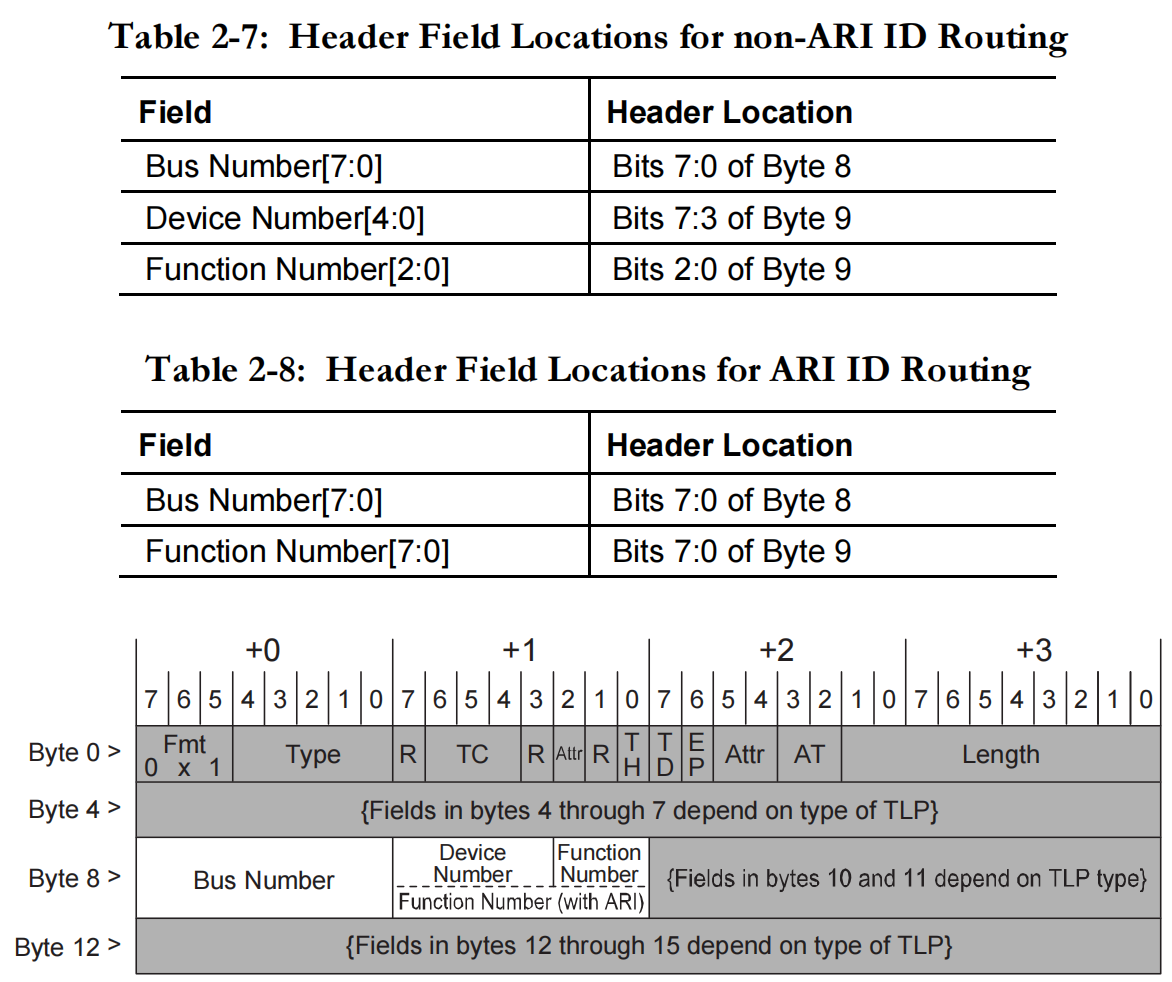

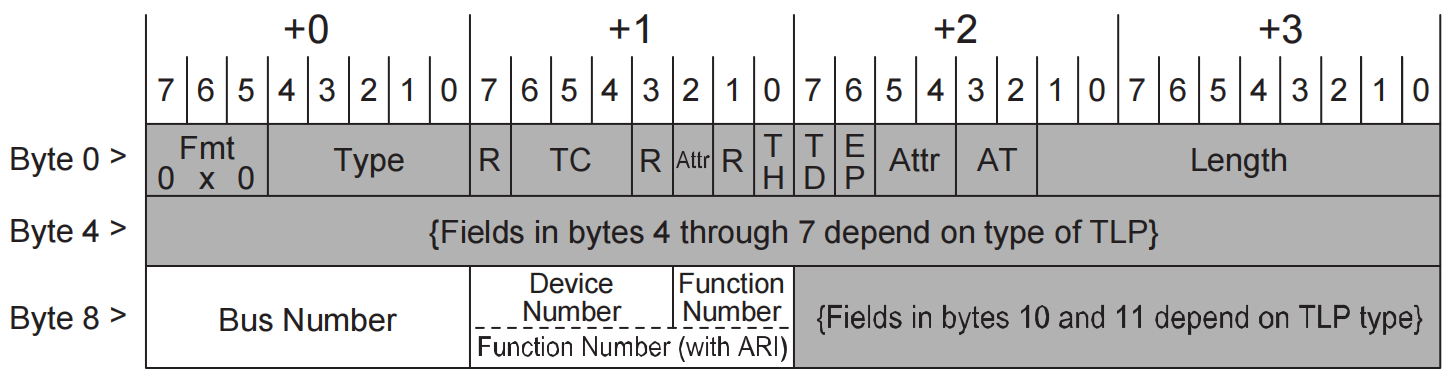

也正因为如此,所以当采用ID路由时,BDF中的Device Number实际上是0,所以有了一种替代ID路由的另一种路由方式,称为ARI(Alternative Routing-ID Interpretation)。也就是把device Number作为了Function Number,每个PCIE设备可以具备256个功能。

欢迎关注公众号点击【资料下载】领取相关资料

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我