3.1 先粗浅的了解下内存映射再说PCIE

内容简介

2024-01-21

全文共1212字,阅读大约需要4分钟,在本章节主要介绍PCIE的配置和路由相关内容,这部分内容就涉及与CPU交互的内容,二者就有了内存映射相关内容,所以本节就粗浅的理解一下,方便后文的叙述。

01

对于用过IMX6U或其它处理器的朋友来说,地址映射的概念还是很好理解的,但如果专注与FPGA开发的话,可能是个不得不体会一下的概念。

为什么需要理解地址映射呢?因为最早的PCI协议是inter提出来的一种CPU与外设进行数据交互的实现机制。PCIE是PCI的延申和发展,所以打满了适配CPU的烙印,而CPU与外界进行数据交互的基础就包括地址映射,所以理解地址映射有助于我们理解PCIE的一些处理机制。

02

这其实涉及到了计算机体系结构,我们这里就简单粗浅的介绍一下。简单来说就是CPU(Central Processing Unit,中央处理单元)通过地址映射(Address Mapping)的方式来访问外设,这是CPU运行的规则。有一本书叫《编码的奥秘》非常通俗易懂的介绍了从摩斯密码到计算机的演化过程,挺有意思。

比如一个CPU是32位的,可以理解它拥有0到2^32-1这么多个工厂。每个数就是每个工厂的地址,所以说32位系统寻址范围是4G。例如有个工厂,他的地址是0X020E005,这个工厂干得活就是控制一个灯的亮灭,给这个工厂输入指令1灯灭发送0灯亮。那我们可以给0X020E005这个地址写0让灯亮,写1让灯灭。 然而每个工厂的规模太小,能干的活太少,我们就可以联合办厂,把多个工厂合起来共同生产一个东西,例如控制IIC、DDR等等就是多个地址来控制。

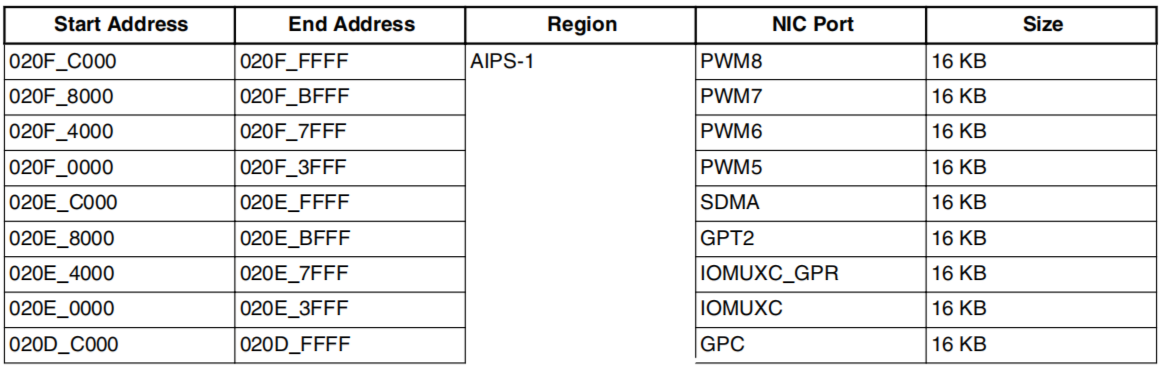

我们根据需求来定义CPU每个工厂的工作内容,是否几个工厂要联合起来。而工厂我们可以抽象为32bit的数字,就好像手机号码,也就是地址,方便管理。我们把支持不同功能的工厂罗列出来,形成一个功能列表,就得到了地址映射表了,如下图是IMX6U处理器的一部分地址映射,可见都是几个地址合起来实现一个功能。

03

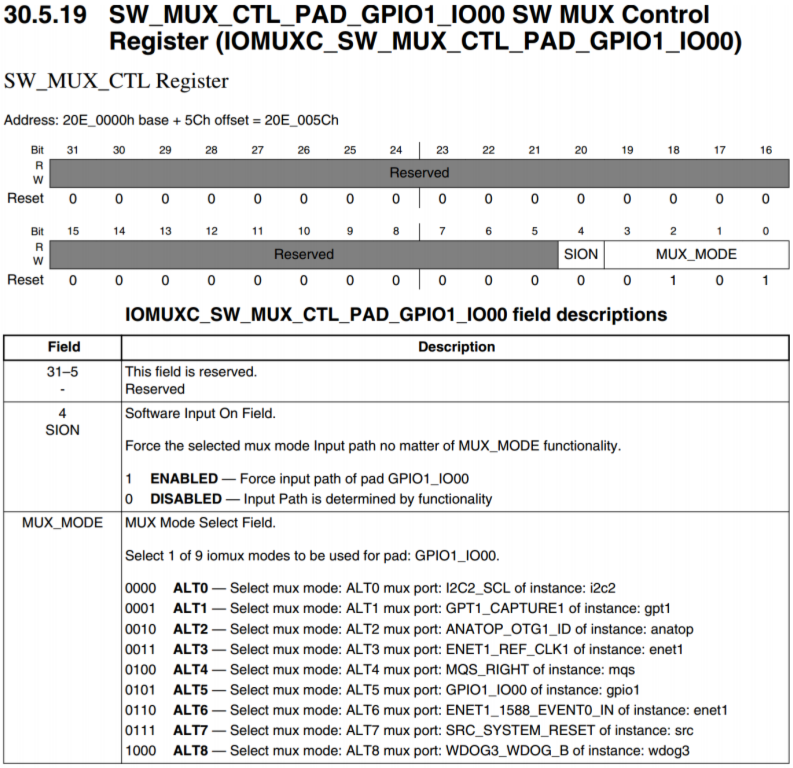

如下图是名为IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00 的寄存器, 寄存器地址为 0X020E005C,这个寄存器是 32 位的,但是只用到了最低 5 位,其中 bit0~bit3(MUX_MODE)就是设置 GPIO1_IO00 的复用功能的。GPIO1_IO00 一共可以复用为 9 种功能 IO,分别对应 ALT0~ALT8,其中 ALT5 就是作为 GPIO1_IO00。GPIO1_IO00 还可以作为 I2C2_SCL、GPT1_CAPTURE1、ANATOP_OTG1_ID 等。所以我们需要对地址020E005C写个0x5;

04

上述这个举例我们称之为内存映射I/O(MMIO,Memory-Mapped Input/Output),通过将I/O设备的控制寄存器映射到存储器地址空间中,来简化硬件设计和软件访问,也就是IO地址空间访问。还有一种叫做存储器地址空间访问,就说有些工厂没有具体的功能,破产了成了仓库,用来放数据的。把这些工厂的地址按序排列,就说一段存储空间了,把这段空间映射到外设的一段存储区域,那就是存储器地址空间访问了,PCIE的BAR寄存器差不多就这意思。

这只是粗浅的理解,实际上还有非常复杂的机制来配合。那为什么要这样做呢?为什么不直接控制我们想控制的外设呢?主要原因是更高效、更灵活、更安全,CPU完全隔离了外设的差异性,通过统一的编程方式就可以轻松访问控制,更不需要在意时序这样的细节,更利于基于操作系统完成复杂的事务。所以也是这种架构发展的必然结果。

PCIE也是CPU的外设,所以对PCIE的控制也是这种方式,然而PCIE也描述一种连接方式,接口为PCIE的外设的类型和数量都是可定制的,对此有增加了控制和统一的难度。这就引出来了下一节的内容,CPU是如何访问PCIE外设的。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我