2.3来分析一下PCIE事务层的通用帧头(二)

内容简介

2024-01-21

PCIE事务层帧头分为通用部分和不同事务的特有帧头两部分。本篇主要是介绍PCIE事务层通用帧头剩余部分,

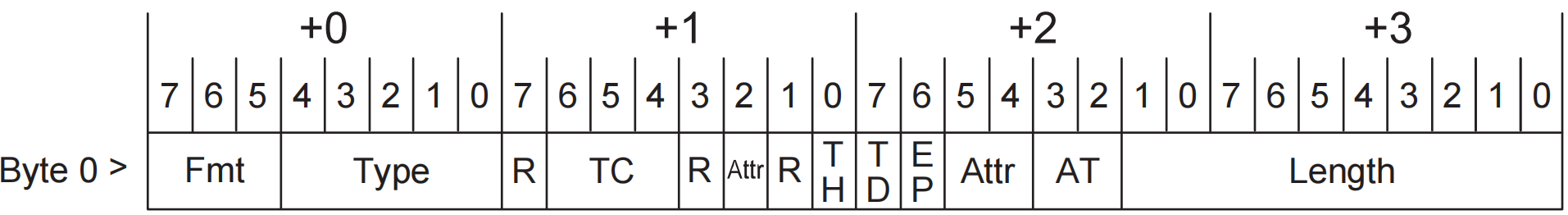

如下图是所有TLP数据包所具有的帧头,也就是最前面的32bit。在上一节,我们介绍了FMT、TYPE和TC,在本节就把剩下的都介绍了。

01

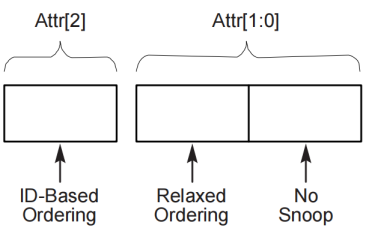

Attr

Attr是Attributes的缩写,属性的意思。人家协议给了这样一个图,我们就先搞明白这仨表示什么吧。

1

ID-Based Ordering

说白了就是保序。这是PCIE总线的一种数据传输和控制机制,主要用于优化和控制数据包在PCIE总线上的传输效率。PCIE有种路由方式叫ID路由,采用Bus Number、Device Number和Function Number(BDF)来确定目标设备的位置。每个PCIE设备都有唯一的ID,通常由设备的物理位置和逻辑配置决定的。

ID-based Ordering 机制确保具有相同源 ID 和目的 ID 的数据包按照它们被发出的顺序到达。这意味着,如果两个数据包来自同一个发送者并且目的地也相同,那么它们将会按照发送顺序进行传输和接收。

通过保持特定通道上数据包的顺序,ID-based Ordering 可以减少需要的缓存和重新排序操作,从而提高数据传输的效率。在出现错误或数据丢失的情况下,ID-based Ordering 也有助于快速定位问题,因为数据包的顺序性提供了额外的上下文信息。

2

Relaxed Ordering

这是PCI-X总线的一种特点的总线事务的处理特性,用于处理并发的数据交换,目的是提高总线的性能。Relaxed Ordering我们可以翻译为松散排序,这种松散排序允许传输的数据在特定情况下不必严格安装发起顺序来处理,也就是说允许一定程度上的乱序,这样可以减少由于严格排序所引起的性能瓶颈。

3

NO Snoop

首先得了解下Snoop的意思,通常是对系统内存内容的监视或检查,主要用于缓存一致性中的。那么何为缓存一致性呢?在多处理器系统中,每个处理器可能都有自己的缓存。为了保持所有处理器之间的数据一致性,系统需要确保一个处理器的缓存更新能够被其他处理器感知到。这就是通过 "Snoop" 操作来实现的。尽管 "Snoop" 操作对于维护数据一致性是必要的,但它也可能引起性能损失,因为它需要额外的内存访问和处理器间通信。

在 PCIe 中,"No Snoop" 属性可以被设置在特定的数据传输上。当这个属性被激活时,它指示系统不进行 "Snoop" 操作,即不监视或检查这些数据传输对应的内存内容。通常用于不需要缓存一致性维护的数据传输。然而,正确地使用 "No Snoop" 属性需要对应用程序的数据共享和一致性需求有深入的了解。不当的使用可能会导致数据不一致或其它问题。

明白这仨是啥意思了,也就好理解如何使用了。对于ID-Based Ordering和Relaxed Ordering这俩属性,协议做出了如下指示。

1、Attr[1](Relaxed Ordering)对于配置请求、I/O请求、消息请求和作为消息中断的内存请求是不适用的。

2、Attr[2](ID-based Ordering)对于配置请求和I/O请求需置零。

3、Attr[0]如上文解释同样对配置请求、I/O请求、消息请求和作为消息中断的内存请求不适用。

02

TH

这是一个标志信号,位宽1bit,表示当前 TLP 中含有 TPH(TLP Processing Hint)信息。TPH 是 PCIe V2.1 总线规范引入的一个重要功能。用来表示通知接收端即将访问数据的特性,以便接收端合理地预读和管理数据,其实也是针对CPU的缓存架构提出的一种提升性能的技巧,例如数据很快被使用,就别放到低速缓冲区例如硬盘,而是放到高速缓冲区上。但TH只是一个开关,或者是粗略的控制,具体还得有其他信号一块搭配。

03

TD和EP位

TD表示TLP中的TLP Digest是否有效,为1表示有效,为0表示无效。而EP位表示当前TLP中的数据是否有效,为1表示无效,为0表示有效。

04

AT

AT是Address Type的缩写,AT字段与 PCIe 总线的地址转换相关。看《PCIE导读》上说只有在支持 IOMMU技术的处理器系统中,PCIe 设备才能使用该字段。此外AT字段可以用作存储器域与PCI域之间的地址转换,也可以用于方便多个虚拟机共享同一个PCIE设备。这个现在也搞不明白,还是先知道是地址转换相关就这样吧。

05

Length

Length 字段用来描述 TLP 的有效负载(Data Payload)大小。 PCIe 总线规范规定一个 TLP的 Data Payload 的大小在0B~ 4096B之间。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我