3.6 一起了解下PCIE的TYPE00配置空间

这是剖析PCIE协议的第16篇文章

内容简介

2024-01-26

本文主要介绍type0/type1 header的各个字段含义,这篇大概瞅瞅就行了,后续用到自然晓得了

由于PCIE要兼容PCI,所以Header部分一样,但很多内容对于PCIE是不需要的,所以本文就介绍PCIE需要的内容,不需要的就不说了,省的增加不必要的学习成本。

01

Type00的Header介绍

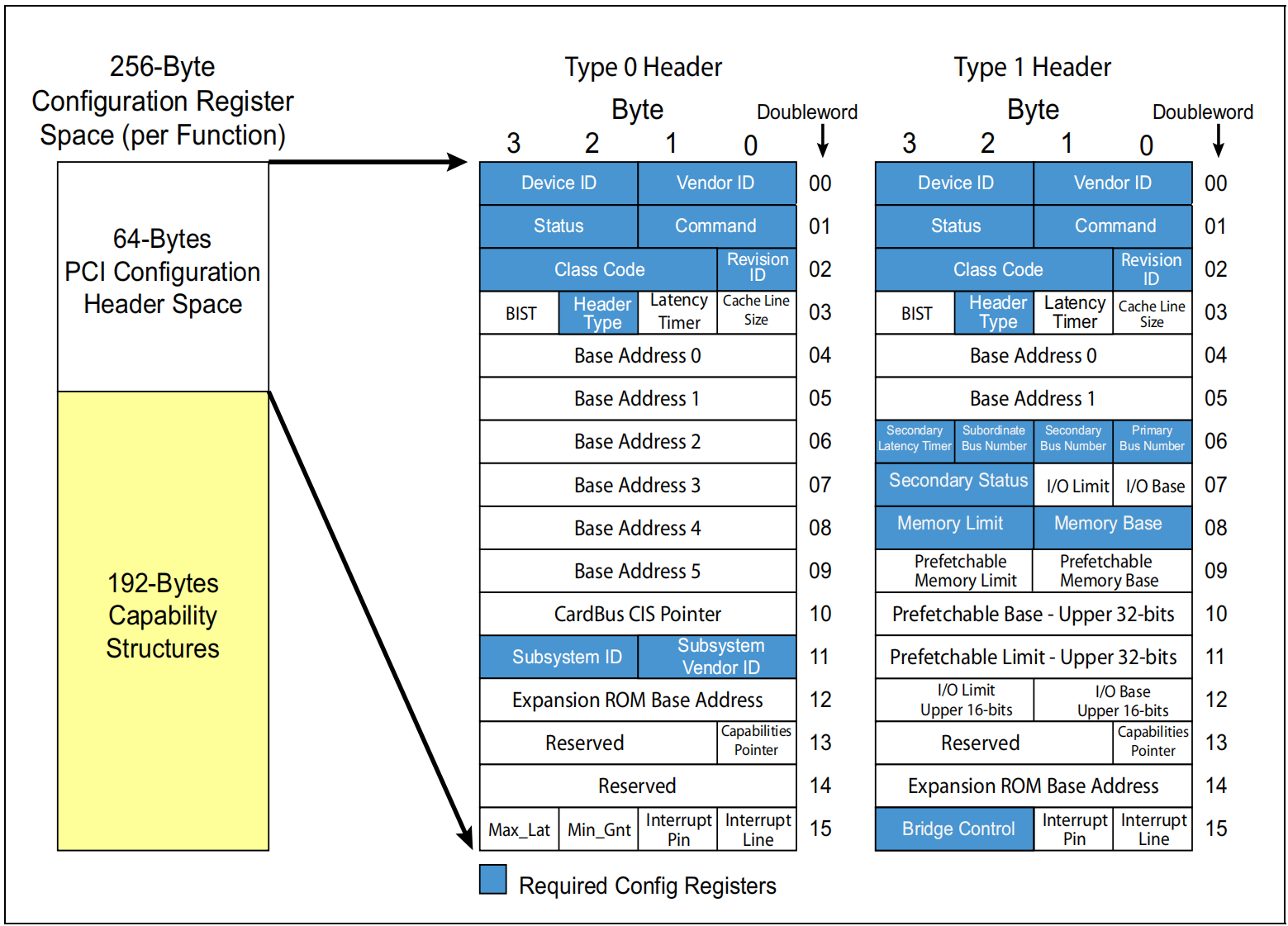

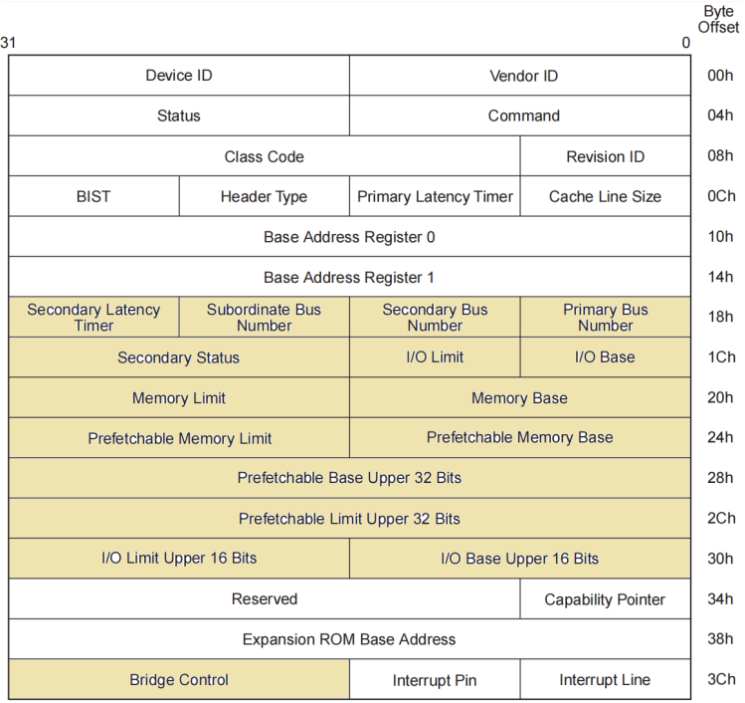

PCIE或者PCI的配置空间有一部分是一致的,就是Type header,64字节,16DW,分为Type0和Type1两种。Type01用于PCI桥,Type00用于PCI设备,由于二者的功能不同,所以根据实际需求做了区分。剩余的192byte是根据设备的实际需求可自定义的。总共是256byte(64DW),是否还记得CFG_ADDR的Register_Number的位宽是多少?6bit可寻址范围是0到63,也就对应这256byte配置空间,每次可访问其中的32bit。等到了PCIE,有了MMIO机制,每个功能的配置空间扩展到了4KB,但Header部分都还是一样的。

本文先介绍TYPE00,也就是PCIE设备(EP)的配置header,如下图所示。

01

这两个值由PCISIG(eripheral Component Interconnect Special Interest Group)分配,只读。Vendor ID代表PCIE设备的生产厂商,Device ID代表这个厂商所生成的具体设备。

02

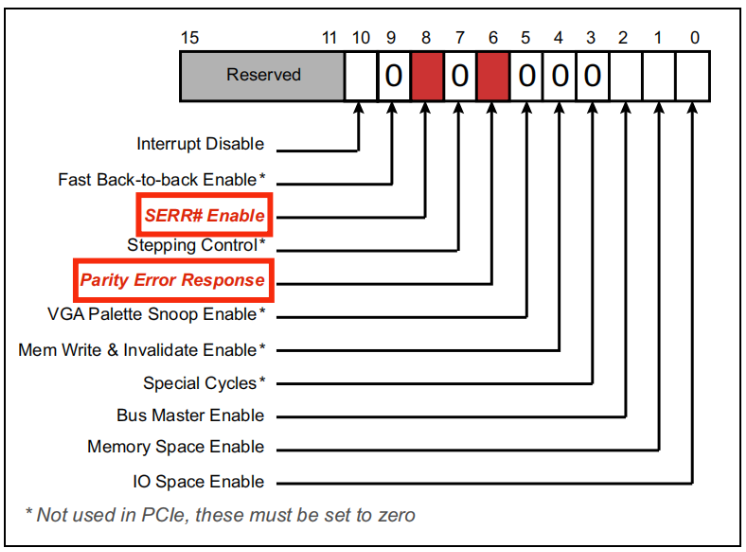

这是PCIE设备的命令寄存器,在初始化时其值为0,此时只能接受配置请求事务,需要对该寄存器配置才能访问该设备的存储器或者I/O请求。如下图是比较形象的展示了每个bit位的作用,其中标*的表示不适用于PCIE,必须置为0。

bit8

SERR# Enable

如果置位会发送ERR_FATAL和ERR_NONFATAL错误消息给到RC

bit6

Parity Error Response

在接下来要介绍的状态寄存器中由一位叫做“Detected Parity Error”,表示是否存在奇偶校验错误,而这个bit位如果置1,则使能奇偶校验的检测,如果置为0,则不使能奇偶校验的检测。对于PCIE和PCI设备来说,功能是一样的。

03

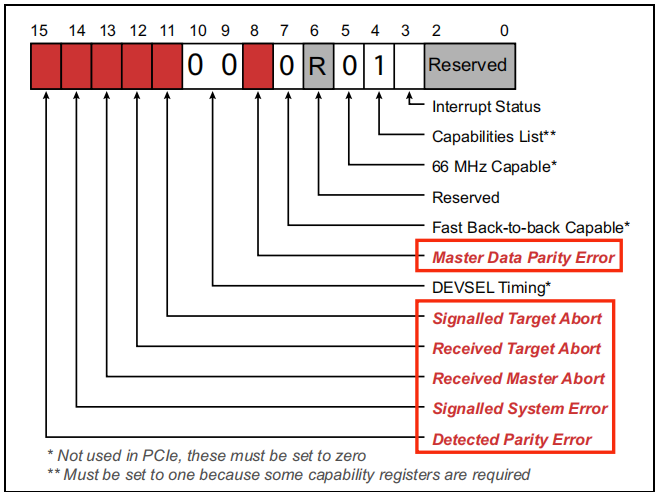

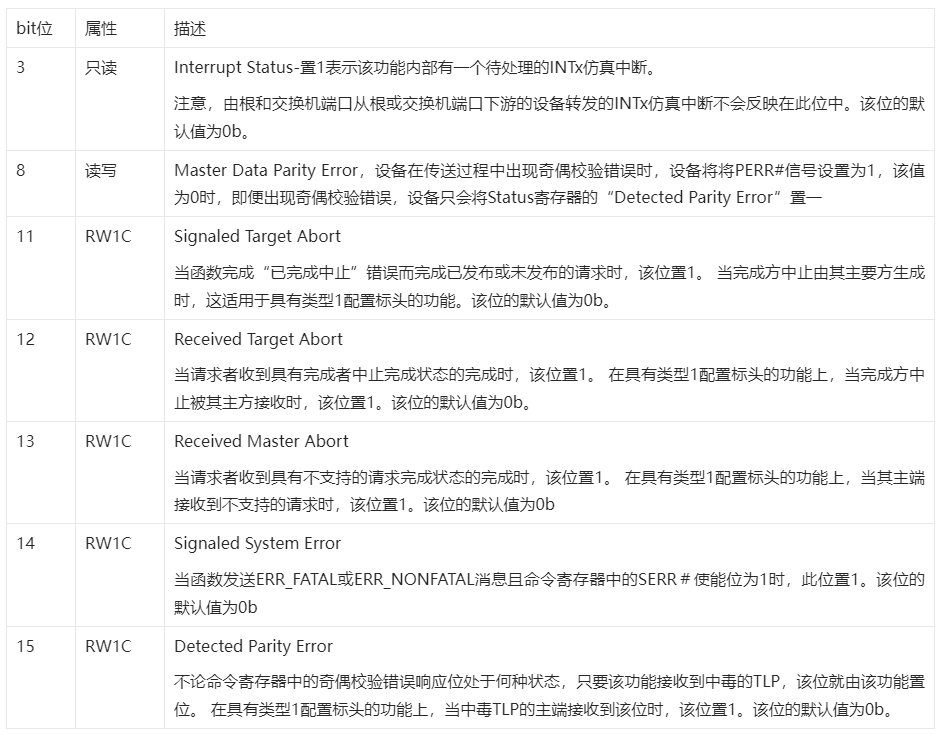

如下图是状态寄存器,一共16bit,每bit的含义如下所示,同样标有*的bit位不适用PCIE。

04

修订板(扩展)ID寄存器,就是版本号。它的值由功能制造商指定,用于确定该功能的修订版本号。

05

这是类代码寄存器,记载PCI设备的分类,可供系统转接进行不同设备的识别,该寄存器由三个字段组成,分别为Base Class Code、Sub Class Code和Interface。其中Base Class Code将设备分为显卡、网卡等设备,Sub Class Code则是对这些设备进一步细分,Interface定义接口。

06

记录HOST处理器使用的Cache行长度,PCIE也用到了,可以判断与Cache行的对应关系。

07

PCIE置零

08

只读寄存器,由8bit组成,bit7=1表示当前PCI设备是多功能设备,为0表示为单功能设备,bit6~0表示当前配置空间类型。

09

BIST字段都提供了设备自检的信息,支持完整性检查,等后续如果写道了看看具体怎么用的。

10

这个是个比较关键的内容,后面会有专门的一篇文章来讲述,我们一般简称bar寄存器,用来保存在内存空间的基地址的,一个设备可以最多申请6个基地址空间。也就是说设备可以在内存中申请一片内存区域,这个bar寄存器就保存了这片内存区域的基地址和大小。

11

这个是用来记录使用的Cache行长度的,对于PCIE是没有意义的置0。

12

记录设备的生产厂商和设备名称。是扩展用的,如果上面的ID无法区分可用这部分的。

13

对于PCI设备,在处理器还没有运行操作系统之前,就需要完成基本的初始化设置,比如显卡、键盘和硬盘等设备,为了实现这个“预先执行”功能,PCI设备需要提供一段ROM程序,处理器在初始化过程中将运行这段程序,初始化些PCI设备,这个即记录了这段ROM程序的基地址。

14

这个对PCIE挺有用,Capability Pointer存放Capabilities寄存器组的基地址,可以访问扩展的配置信息,后面会专门介绍。

15

是系统软件进行配置时写入的,记录当前设备使用的中断向量号

16

中断引脚寄存器是一个只读寄存器,用于标识功能使用的旧式中断消息(更多信息,请参见第6.1节)。有效值为01h,02h,03h和04h,分别映射到INTA,INTB,INTC和INTD的旧式中断消息。值00h表示功能未使用旧式中断消息。

17

不适用于PCI Express,置零

02

Type01的Header介绍

如下图是PCI桥配置空间里面的Header部分,除标有颜色外,其它的均与PCI设备一致

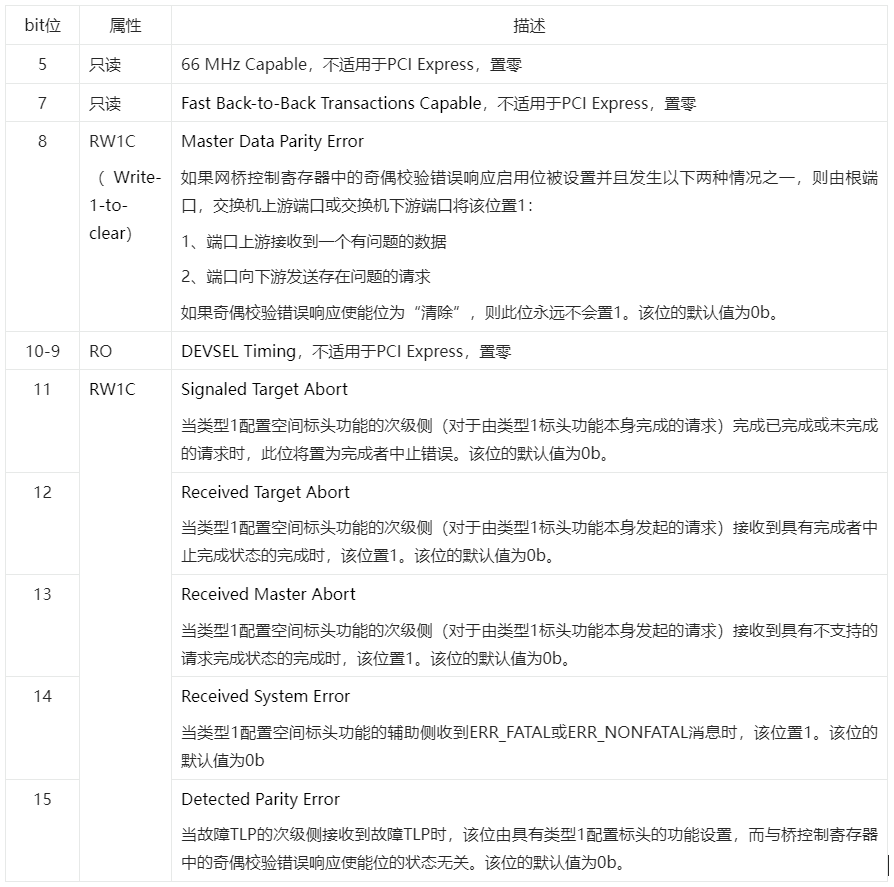

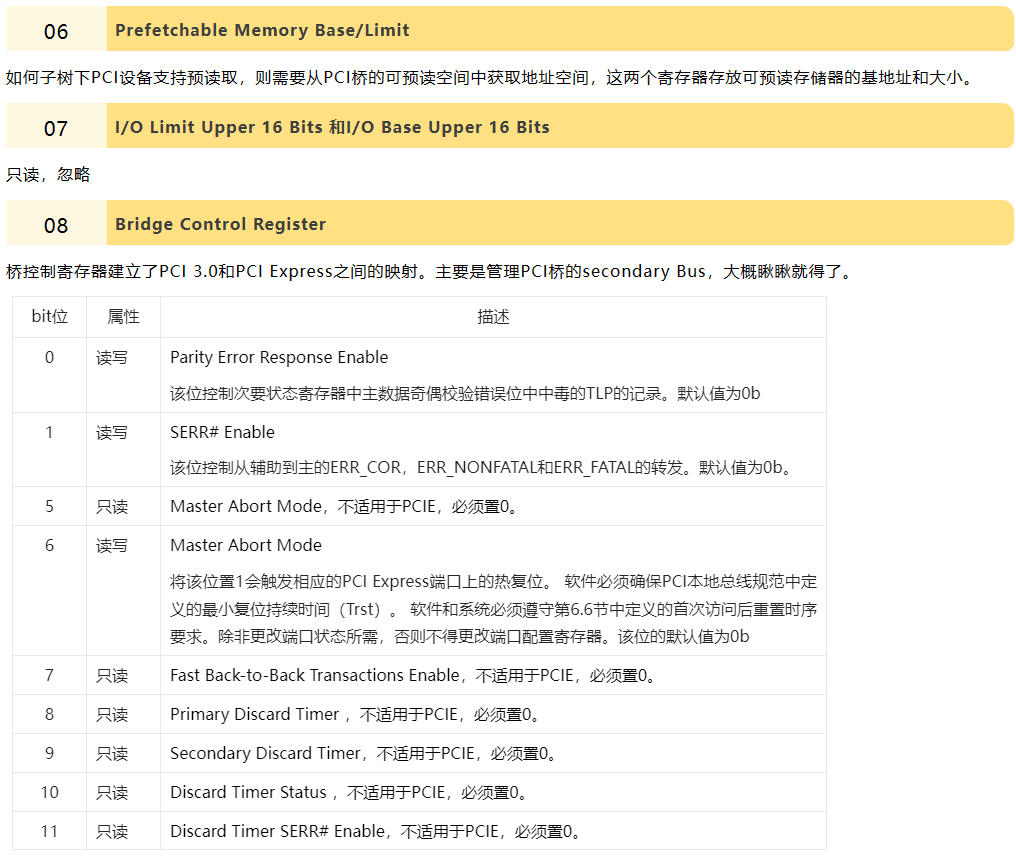

01

这仨也就是3.2提到的用于HOST主机进行数据路由的依据,而且在操作系统上电初始化阶段,主机惠帝PCI总线树进行遍历,以了解其拓扑结构,此时会根据遍历结果将这仨置为,如果没有对应设备则置0。其中

1、Primary Bus Number :当前PCI桥的上游总线号

2、Secondary Bus Number :当前桥的总线号

3、Subordinate Bus Number:存放当前PCI子树中,编号最大的PCI总线号,也就是一个分支里面最深最靠下的总线号,但不一定是整个拓扑里面最大的。

05

PCIE的内存事务采用地址路由,这两个寄存器存放所有这些PCI桥所在分支的设备使用的存储器地址空间集合地址和大小,用于地址路由,也会在后文提到。

欢迎关注公众号点击【资料下载】领取相关资料

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我