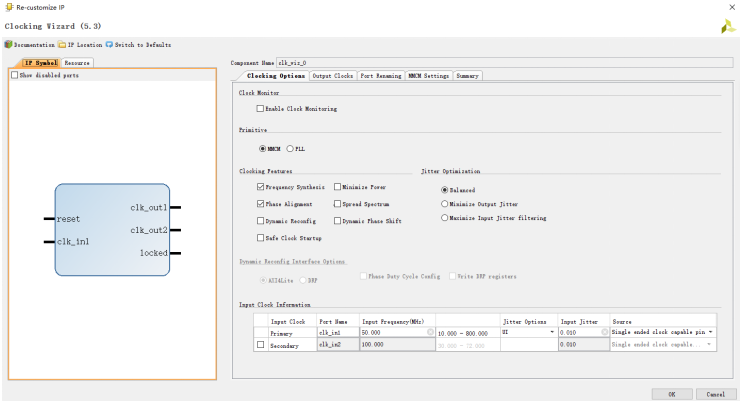

IP核例化的第一部分

Clocking Wizard就是用来产生不同频率、相位甚至占空比的IP核。该核对每一个FPGA开发中可以说是再熟悉不过了,故本文仅对该核在配置过程中的选项卡内容进行简单的阐述。

第一部分 :Clocking option

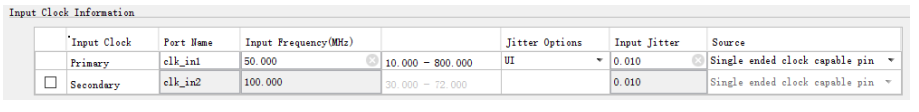

这部分是用来配置时钟网络功能和输入时钟的。

1、Enable Clock Monitoring

Monitoring具有检测的意思,使能该选项就是可以最多监视4个时钟,监视输入频率是否超出渔区频率范围,检测时钟是否停止是否存在毛刺。

2、Primitive

这是选择调用的硬核资源是MMCM还是PLL,一个CMT上既有MMCM也有PLL,PLL是MMCM的一个子集,在绝大多数情况下,如果需要两个锁相环,我们可以调用一个MMCM一个PLL,这样保证时钟来自同一个BANK。

3、Clocking Feature

我们可以看到有7个时钟功能选项,这些其实就是与原语的一个封装调用。

Frequency synthesis:

这是必选项,如果不选就无法产生于输入时钟不同频率的时钟了。

Phase alignment:

此功能允许将输出时钟锁相至参考时钟,实现相位对齐。

Dynamic reconfiguration:

动态重配置,也就是调用硬核的重配置功能,对外接口可以是AXI4-Lite也可以是DRP接口。

安全时钟启动和排序

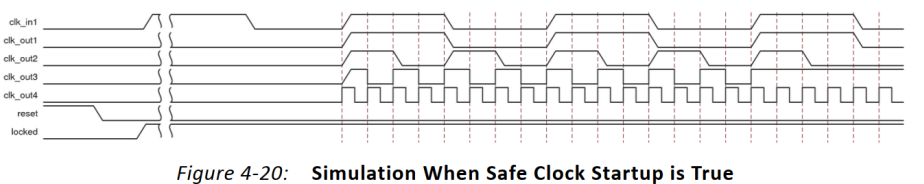

Safe Clock Startup:

此功能对于在输出端获得稳定有效的时钟很有用。安全时钟启动功能可在8个输入时钟被采样为“高”后,使用BUFGCE在输出上提供稳定有效的时钟。排序功能可根据通过GUI输入的数字按顺序启用时钟。 顺序使能的两个输出时钟之间的延迟是顺序时钟中第二个时钟的8个周期。此功能对于需要模块一个接一个地运行的系统很有用。

Minimize power:

该功能以可能的频率,相位偏移或占空比精度为代价,将芯片所需的功率最小化。选择“扩频”功能后,此功能不可用

Spread Spectrum (SS)

此功能提供调制的输出时钟,可降低电子设备产生的电磁干扰(EMI)的频谱密度。 此功能仅适用于MMCM(E2 / E3)原语。当扩频为TRUE时,Minimize power和Dynamic reconfiguration功能不可用。

Phase alignment

此功能允许将输出时钟锁相至参考,例如设备的输入时钟引脚

3、Jirtter Optimization

Balanced:

选择“平衡”会导致软件选择正确的带宽来优化抖动。

Minimize output jitter

此功能可最大程度地减少输出时钟上的抖动,但会降低功耗,并可能会产生输出时钟相位误差。 此功能不适用于“最大化输入抖动过滤”。

Maximize input jitter filtering

此功能允许输入时钟上更大的输入抖动,但会对输出时钟上的抖动产生负面影响。 此功能不适用于“最小化输出抖动”。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我