CMT、BUFH、BUG介绍

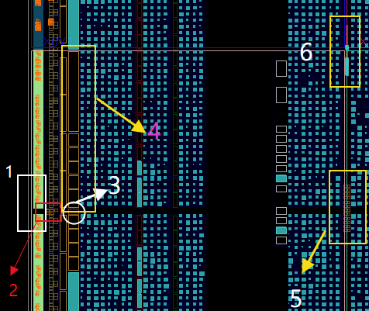

继续根据下面这图来介绍:

三、CMT

黄色方框圈住标有4的这部分称之为CMT,即clock management tiles 的缩写,每个BANK都有一个,这里面主要包括了一个MMCM和一个PLL,PLL可以理解为是MMCM的子集,都是可以视为锁相环,用于产生不同频率、相位的时钟以供使用,具体接口介绍会在第四、五章介绍。

四、BUFH

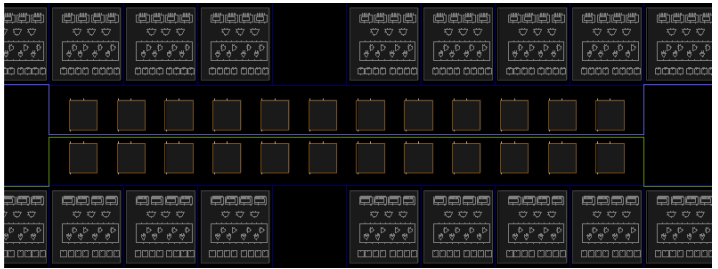

黄色方框圈住标有5的这部分部分是区域水平时钟缓冲器BUFH,原本人家是竖着的,但太占地我就让它躺下了。经过该BUF的时钟只在本区域有效,其中H是Horizontal的缩写。每个BANK有12个BUFH,它们位于BANK的一侧,且在水平中间位置排成一列,所以下图是左右相邻两个BANK的BUFH。

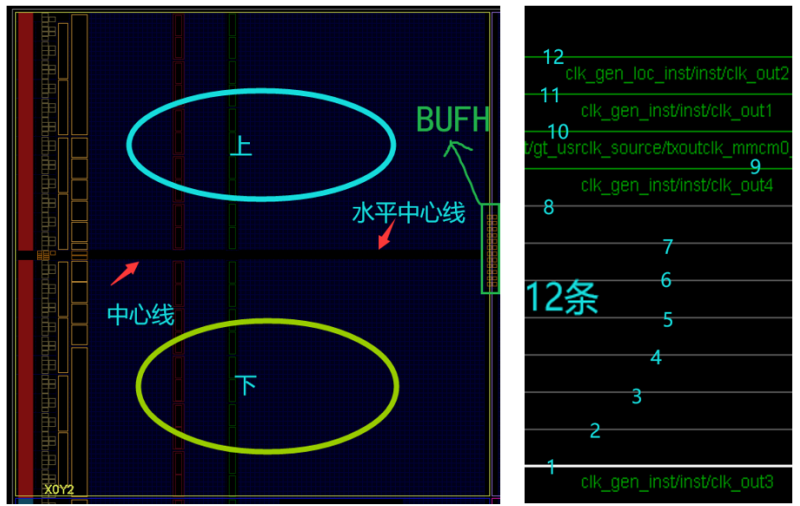

如下图是一个BANK的整体,BUFH可以驱动同一BANK的所有资源,我们可以看出“上”和“下”是对称分布的,BUFH位于BANK的一侧垂直居中,中间的分割线是有12条水平时钟线,与12个BUFH相连。BUFG也是通过连接到BUFH进而通过这12条水平时钟线驱动整个BANK的逻辑资源。每个BANK资源是按照一定的规律进行排列,也就是每列有50个CLB、50个引脚、10个BRAM,它们均匀的分布在水平时钟线两侧。不同型号芯片每个BANK的资源是不一样的,但每列资源确实固定的,只不过行数的多少。

5、BUFG

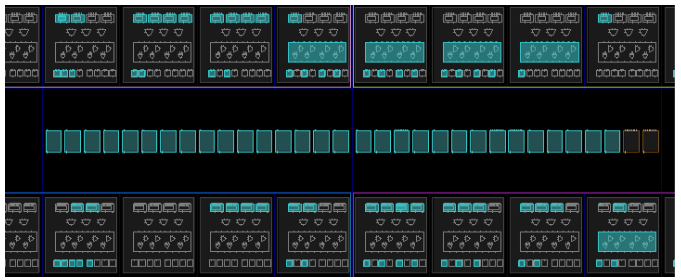

黄色方框圈住标有6的是全局时钟缓冲器,如下图所示,由于水平放置太占地,我也让它躺倒了,一竖溜有32个,而且每个芯片都会有32个BUFG。它是我们用的最多的时钟buff,经过BUFG的时钟可以连接到任意资源上去,BUFG不仅可以实现时钟缓冲,还有时钟选择、控制等功能。

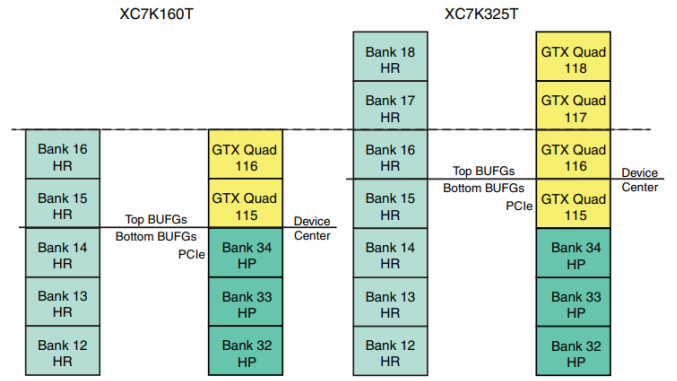

BUFG从竖直方向看位于中间,两侧类似对称形式分布,从水平方向看是尽可能的位于中间,由于BANK数量原因,可能是偏下些,在ug472中也有下图为我们举例说明。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我