MMC的接口信号介绍(二)

9、LOCKED

MMCM / PLL的输出,用于指示MMCM / PLL在输入引脚上何时实现了参考时钟和反馈时钟的相位和频率对准。 相位对齐在预定义的窗口内,频率匹配在预定义的PPM范围内。

MMCM上电后自动锁定,不需要额外的复位。 如果输入时钟停止,违反相位对齐(例如,输入时钟相移)或频率已更改,则在一个PFD时钟周期内将LOCKED置为无效。 解除锁定时必须复位MMCM / PLL。 在声明LOCKED之前,不应使用时钟输出。

10、CLKIN1/2

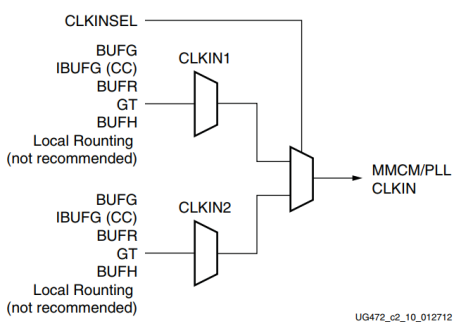

CLKIN1是主要参考时钟输入,可以由SRCC或MRCC I / O直接在同一时钟区域内驱动,SRCC或MRCC I / O可以通过垂直相邻时钟区域内的CMT主干,BUFG,BUFR,BUFH,互连(不推荐)来驱动,或直接通过 高速串行收发器。 当时钟输入来自用于级联CMT功能的另一个CMT模块时,只能使用CLKOUT [0:3]。

CLKIN2是辅助时钟输入,用于动态切换MMCM / PLL参考时钟。CLKIN2可以由SRCC或MRCC I / O直接在同一时钟区域内驱动,SRCC或MRCC I / O通过CMT主干在垂直相邻的时钟区域内进行驱动,BUFG,BUFR,BUFH,互连(不推荐),或直接通过 高速串行收发器。

11、CLKINSEL

CLKINSEL信号控制时钟输入MUX的状态,高= CLKIN1,低= CLKIN2。 时钟切换期间,MMCM / PLL必须保持在RESET状态。MMCM和PLL参考时钟可以通过使用CLKINSEL引脚动态切换。 切换是异步完成的。 时钟切换后,MMCM / PLL可能会丢失“锁定”并自动锁定到新时钟上。 因此,一旦时钟切换,则必须复位MMCM / PLL。 MMCM / PLL时钟MUX切换如图3-10所示。 CLKINSEL信号直接控制MUX。 不存在同步逻辑。

12、PWRDWN

关闭已实例化但当前未使用的MMCM / PLL。 此模式可用于为设计中暂时不活动的部分和/或在某些系统配置中不活动的MMCM / PLL节省功率。 在此模式下不消耗MMCM / PLL功耗

13、RST

RST信号是MMCM / PLL的异步复位。 当该信号无效时,MMCM / PLL将被同步重新启用。

14、PS*

这三个信号是动态相移接口,暂不阐述

15、CLKFBIN

必须直接连接到CLKFBOUT以获得内部反馈或IBUFG(通过具有时钟偏移功能的外部去歪斜引脚),BUFG,BUFH或互连(不推荐)。 对于外部时钟对齐,除了BUFR以外,反馈路径时钟缓冲器类型应与正向时钟缓冲器类型相匹配。BUFR无法补偿

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我