概述及输入时钟

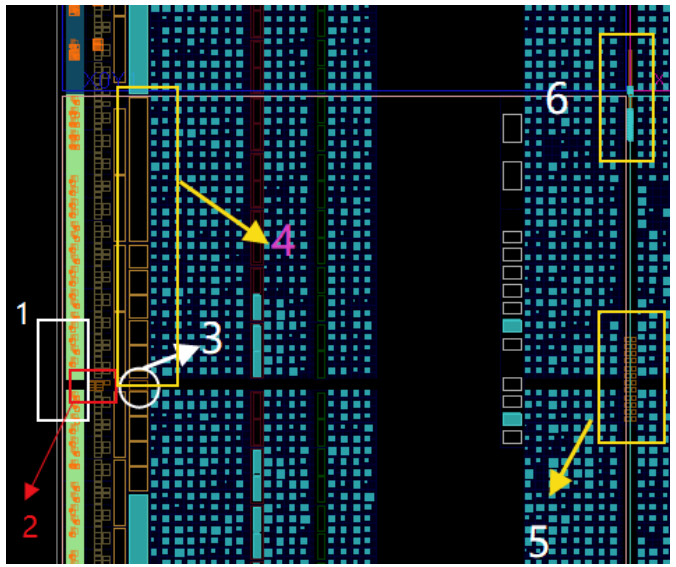

如下图是xilinx的A7芯片的“device”部分截图。时钟相关的主要是下面这几个部分,随便找个工程打开都可以看到如下内容,另外还有高速串行接口的时钟没有表示出来,那个不影响对整体的理解。在图中标有6个地方,这就是包括了FPGA的所有时钟资源(GTPE2_COMMON除外),主要有CC、BUFR、BUFIO、BUFMR、CMT、BUFG和BUFH,下面就对其依次进行介绍。

一、CC

标有1的白色框圈住的内容称之为“CC”,它是“Clock-Capable”即时钟功能的缩写,表示具有时钟功能的引脚,换句话说,并不是所有的引脚都可以接时钟的,有只有通过特定的引脚才能将外部时钟信号引入FPGA内部的时钟资源,这个引脚有两种,分别称之为MRCC(Multi-region clock-capable I/O)和SRCC(Single-region clock-capable I/O)。Multi-region译为多区域,Single-region译为单区域,而者的直观区别在于MRCC可以连接到BUFMR上,但SR不可以,BUFMR具有扩展功能,可以将本BANK时钟引入到其它BANK上,所以称可以连接到BUFMR的CC为MRCC。

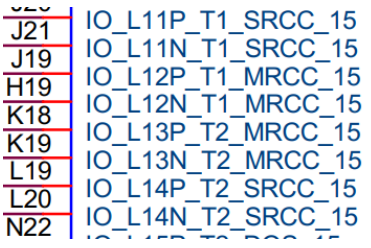

每个BANK有50个引脚,不信你可以数一下,这五十个里面有两对用于SRCC,有两对用于MRCC,如下图原理图所示。它们都是差分的,如果接单端时钟则需接到“P”上,对应的“N”引脚不可用。这些信号可以连接到本bank的BUFR、BUFIO、CMT以及同侧的16个BUFG,这些会在后文阐述。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我