区域时钟-CC和BUFIO

CC

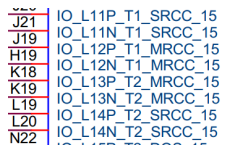

“Clock-Capable”是时钟功能的意思,外部时钟信号必须通过具有时钟功能的引脚接入FPGA,这个引脚称之为MRCC和SRCC。如下图原理图所示,每个BANK有两个MRCC,即Multi-region clock-capable I/O,多区域时钟功能I/O。每个bank有两个SRCC ,即Single-region clock-capable I/O,单区域时钟功能I/O。它们都是差分的,如果接单端时钟则需接到“P”上,对应的“N”引脚不可用。

根据《ug472》第24页介绍,这两种信号可以连接到

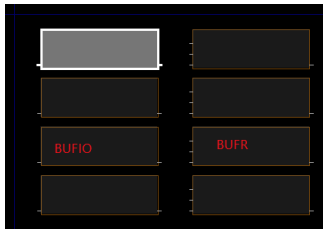

1、同BANK也就是同时钟域的4个BUFIO、4个BUFR和2个BUFMR

2、本BANK或上下BANK CMT的MMCM和PLL

3、连接到16个BUFG,也就是处于同一侧的

4、同时钟域的BUFH

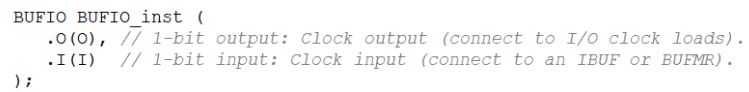

I/O Clock Buffer—BUFIO

每个BANK都有这么四个BUFIO,输入时钟与输出时钟有一定的相位延迟。BUFIO可被MRCC、SRCC、MMCM的CLKOUT0到3、CLKFBOUT以及同一时钟域和上下时钟域的BUFMR驱动,而BUFII仅可驱动IO BANK的ILOGIC和OLOGIC相关时钟,所以BUFIO是区域时钟。因此,BUFIO非常适合源同步数据捕获。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我