CMT的概述

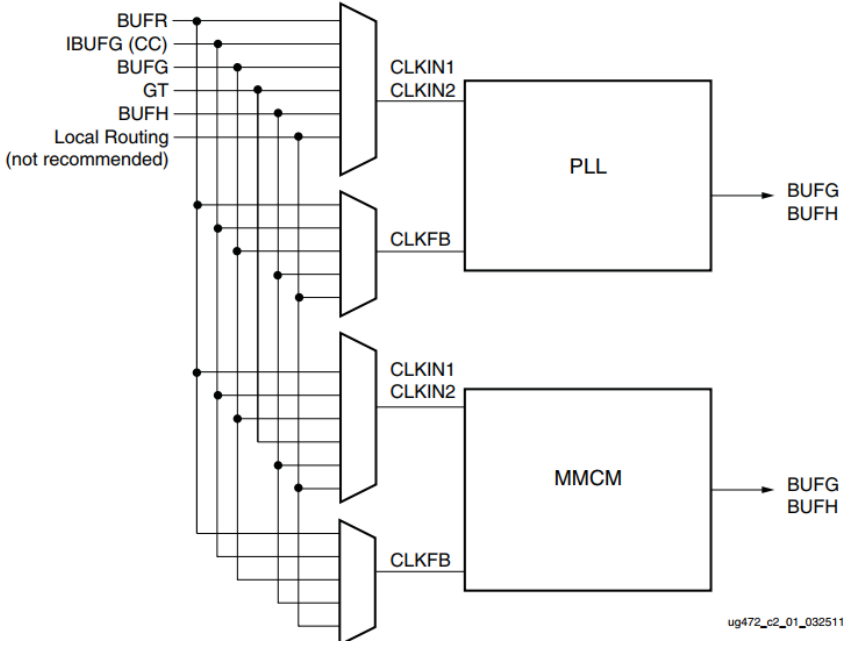

在7系列FPGA中,时钟管理块(CMT)包括混合模式时钟管理器(MMCM)和锁相环(PLL)。PLL可以说是MMCM的阉割版。 每个BANK至多包含一个CMT,具体视芯片资源而定,如下图是CMT的框图,可见输入到CMT也就是PLL或MMCM的时钟可以有多种选择,甚至是本地逻辑路由,但并不建议这样搞,输出时钟会连接到BUFH或者BUFG,这些如果没有特殊要求都会自动实现的。

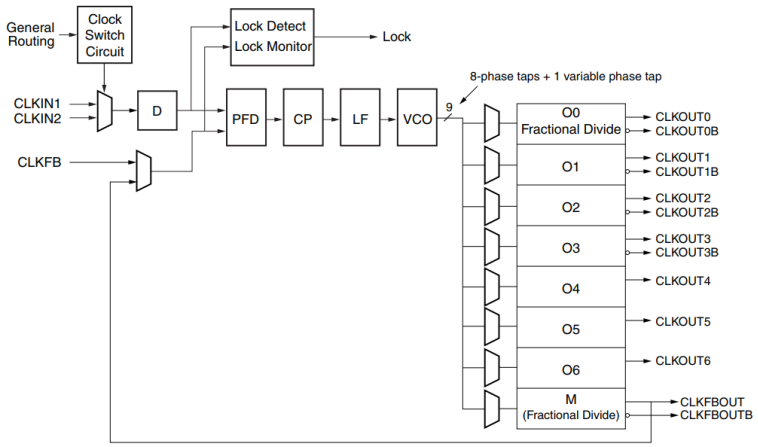

无论是MMCM还是PLL,其功能实现的基本原理是一致的,如下图所示是MMCM产生多个时钟的流程图。每个时钟输入都有一个可编程的计数分配器,也就是“D”,可控制对输入时钟进行分频,PFD是相位检测器,用来比较输入时钟和反馈时钟上升沿的相位和频率进而生成与两个时钟之间的相位和频率成比例的信号,这是一个上升或下降的信号,该信号驱动电荷泵(CP)和环路滤波器(LF)产生VOC的参考电压。当VCO频率过高时,PFD会激活一个下降信号,从而将电压降低,上升信号将增加电压抬高频率。VOC即压控振荡器(Voltage Controlled Oscillator),就是输出频率与输入控制电压有对应关系的振荡电路,有LC和RC压控振荡器,一般用的是RC的。MMCM原理是在VCO输出时钟的基础上可对其进行分频、相位和占空比的调整,已产生我们所需时钟。

CMT具有时钟矫正网络,可实现输出时钟频率与输入时钟频率相位一致,这就为需时钟同步的相关设计提供便利,最起码不需要在这基础上花费时间调整时钟相位,并且具有抖动滤波的功能。我们可以调用相关原语或IP核来实现相关设计。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我