通过CMT是如何实现时钟分频和倍频的

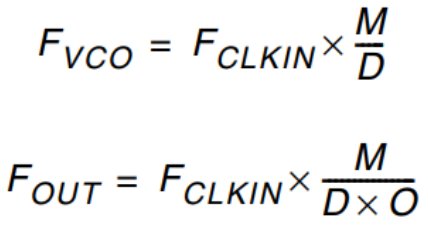

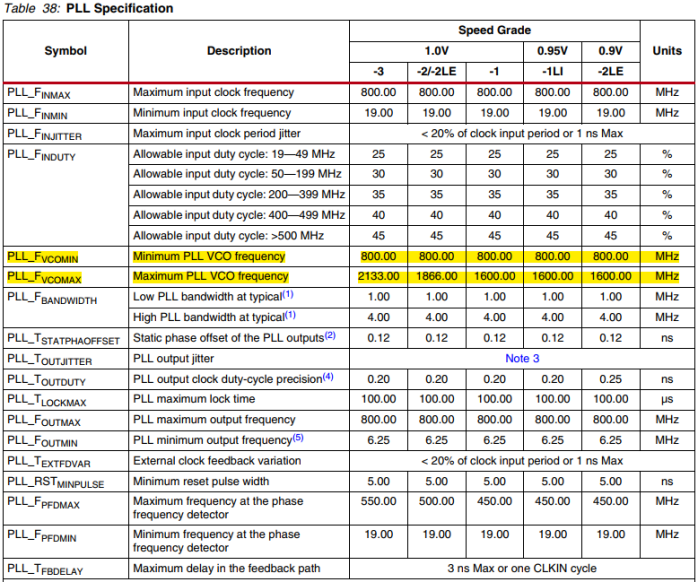

根据上述描述可知,根据CMT产生所用时钟的原理就是首先产生VCO这个基础时钟,然后在其基础上进行分频得到我所需时钟,具体公式如下所示,其中“M”和“D”是可编程控制的,而且CVO的频率也是有限制的,在《DS181》有相关描述,如下表所示。“O”是每路输出时钟对应一个。就CMT内部而言,输出时钟频率的产生有两种情况,一种是仅适用整数除法进行频率合成,另一种是使用小数分频产生所用时钟,为什么要分这两种呢,因为用整数除法我们可以调整时钟占空比,用小数则不能调整,而这个是其内部自动选择的,我们只需知道即可。

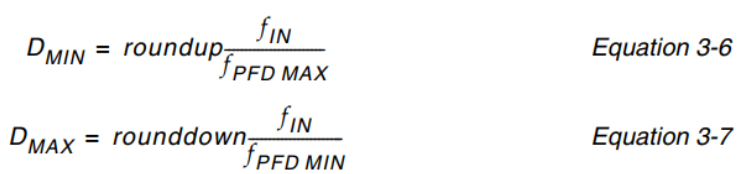

那么我们如何去确定VCO频率呢?在UG472给出了方案,其中PFD是有频率限制的,这在上表中也有描述,例如上表写着不得低于19M,不得高于550或其他。所以由此可以确定D的最大值和最小值,如下

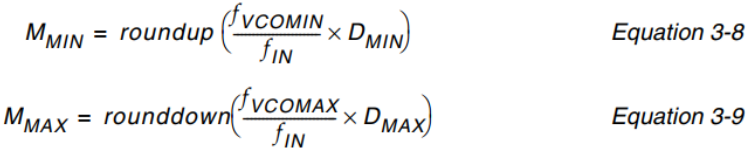

VCO也有频率限制,如上表不得低于800M,不得高于一定值。所以当确定D的值后,M的范围也可大致确定,如下表所示。

当确定D和M的范围后就需要确定其最佳值了。首先确定M的值,这是基于VCO目标频率考虑的,即VCO的理想工作频率。确定方法就是使D和M尽可能的小,同时使ƒVCO尽可能高。

相位的确定逻辑,输出时钟的相位范围是-360度到360度。

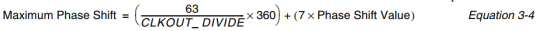

输出时钟相位是可配置的。其内部的实现方案是与VCO有关。CMT内部可以提供8个相移时钟,每个相移45°。始终为0°,45°,90°,135°,180°,225°,270°和315°的相移提供可能的设置。VCO频率越高,相移分辨率越小。所以输出时钟的相位刻度等于45/CLKOUT_DIVIDE。当CLKOUT_DIVIDE小于64时,最大相移是360度,当大于64时最大相移为如下公式所得,也就是相位是由两部分决定的,但在实际编程时我们只需要填写相位就可以了。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我