时钟路由的概述

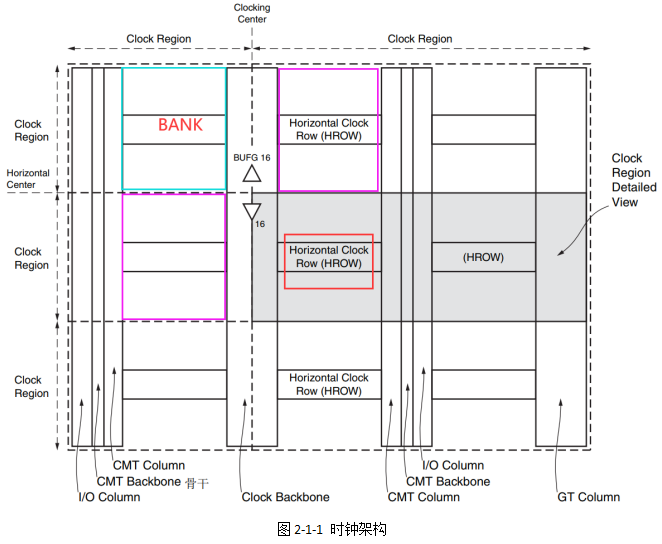

时钟资源包括路由资源和硬核资源,时钟架构是以全局时钟和区域时钟组合搭配而成,总体思路就是以BANK为单元组建区域时钟,以BUFG为纽带连接各个BANK,依次实现模块化的时钟架构。

图2-1-1是《ug472》提供的时钟架构图,自我感觉这图描述得还是有些晦涩。首先我们需要了解下FPGA内部的大致结构,xilinx的FPGA逻辑资源大致可分为两个部分,一部分是I/O BANK,即下图中的“I/O Column”、“CMT Backbone”和“CMT Column”这三部分组成,这里的时钟BUF、IOBUF及I/O LOGIC的不同组合实现FPGA内部数据与外部的交互,另一部分就是以CLB和BRAM为主的资源来实现我们的逻辑功能,不同BANK可能有些其他硬核资源,例如PCIE、XADC、GTP等等。

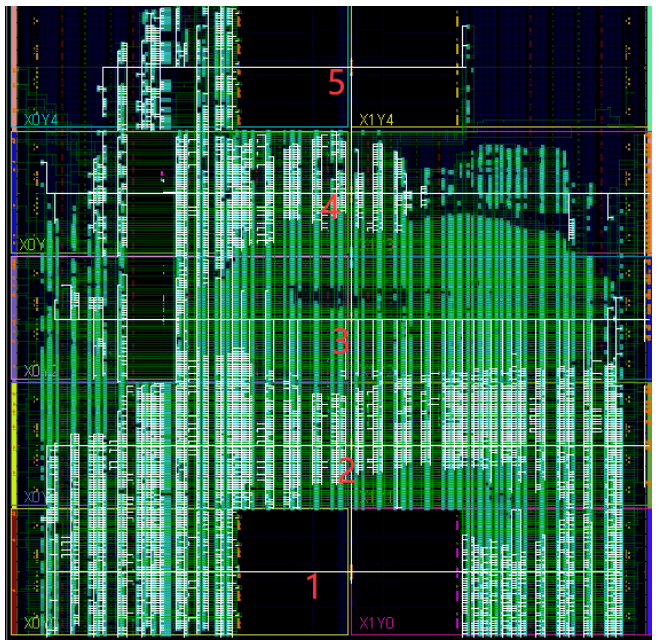

HROW即水平时钟线,也就是在第二章中所阐述的BUFH或BUFG所走的线,由下图我们可以看到,很明显在每个BANK中间有一条白色线,这就是HROW,时钟沿着水平中心线向两侧延伸以为其他器件提供时钟。而左右BANK对称的中心线即为“Clock Backbone”,BUFG在一定长程度上水平分别在“Clock Backbone”中间,一般来讲上部分16个BUFG时钟源来自上半部分的所有BANK,下部分16个BUFG时钟源来自下半部分的所有BANK,而他们的输出可以到整个device的任意位置。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我