7系列selectio之OSERDESE2

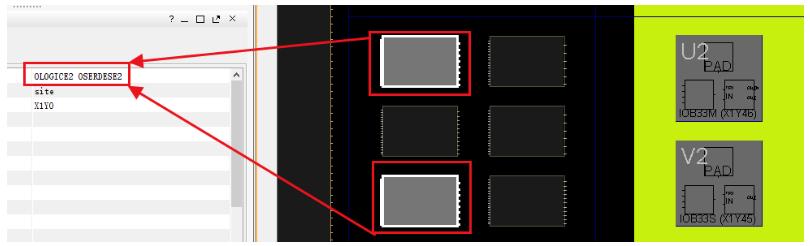

如下图所示,再“device”里面,OLOGICE2和OSERDESE2都是同一个模块,可能是调用里面部分内容实现OLOGICE2功能吧。

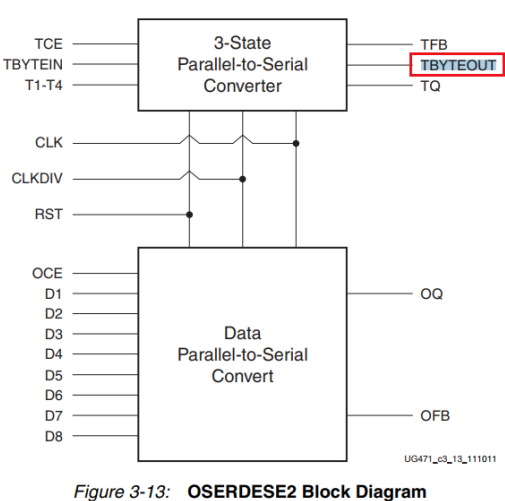

OSERDESE2所实现的功能就是并转串,可以实现SDR模式和DDR模式的转换,而且我们也不需要调用原语,xilinx为我们提供了“selectIO”这样一个IP核,略作配置便可实现相关的功能。本问主要还是结合OSERDES2原语做一个说明,“selectIO”也是调用这个原语的,只不过根据模式选择进行了封装。

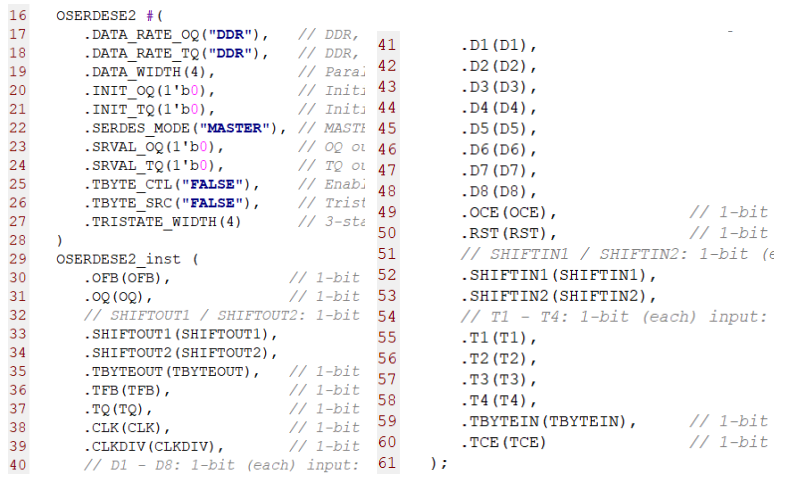

首先来看接口信号:

1、OFB

这个是用来连接到ISERDES2的OFB,实现类似自环的功能

2、OQ

OQ端口是OSERDESE2模块的数据输出端口。输入端口D1的数据将首先出现在OQ。 此端口将数据并行-串行转换器的输出连接到IOB的数据输入。 该端口无法驱动ODELAYE2; 必须使用OFB引脚。

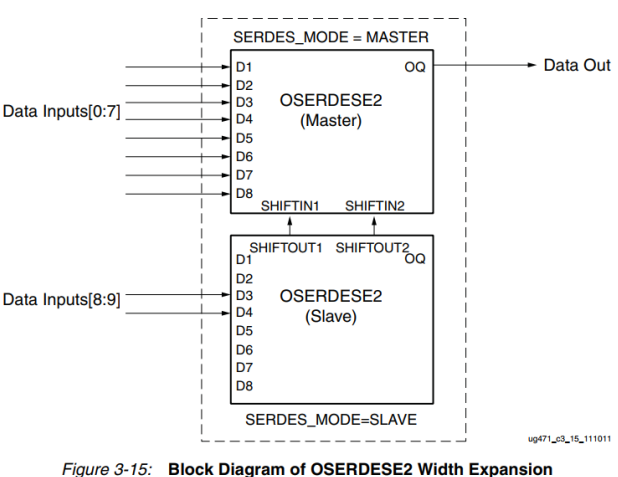

3、SHIFTOUT1/2和12、SHIFTIN1/2

如下图,用来实现扩展功能,

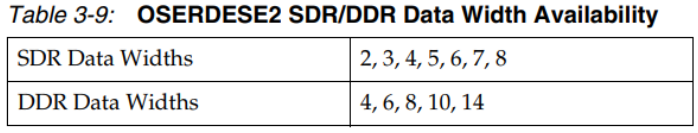

但并不能完全扩展16bit,具体可扩展位宽如下图

4、TBYTEOUT

说是三态输出,在MIG核中用到了。

5、TFB

如果用户需要,此端口是OSERDESE2模块的3状态控制输出,该输出发送到光纤网。 它指示OSERDESE2为3状态。

6、TQ

是OSERDESE2模块的三态控制输出,这个三台输出模块是给DDR3什么用的,一般用户编程是用不到。

7、CLK

串行数据的时钟

8、CLKDIV

并行数据的时钟,与串行数据时钟成倍数关系,具体是由位宽觉得,CLK与CLKDIV需时同相位的,可以来自同意MMCM,或者都是来自BUFG,不能混用。

9、D1~D8

并行数据的输入端口。

10、OCE

高有效数据路径的时钟

11、RST

复位信号,置位后,复位输入将导致CLK和CLKDIV域中所有数据触发器的输出被异步驱动为低电平。

12、T1到T4

所有并行的三态信号都通过端口T1至T4进入OSERDESE2模块。 端口已连接到FPGA架构。 它们可以配置为1位,2位或4位或旁路。 这些端口的行为由DATA_RATE_TQ和TRISTATE_WIDTH属性控制。

11、TCE

这是三态路径的使能信号

接下来看参数部分:

1、DATA_RATE_OQ

模式配置,双沿采样还是单沿采样。即DDR或SDR

2、DATA_RATE_TQ

可以配置为“BUF”、“SDR”、“DDR”这几种模式。其中SDR和DDR即使用并转串模块,而BUF模式,则是使用三态模块,就是用到了T1~4。

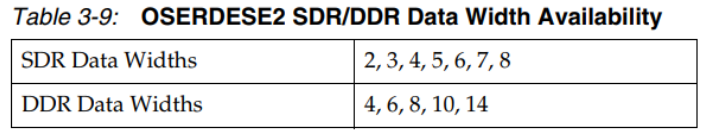

3、DATA_WIDTH

如下图,可以配置这样几种模式。

4、SERDES_MODE

如果扩展,可配置主从模式

5、TRISTATE_WIDTH

当使用三态输入或输出时,用来配置并行端口位宽的。

6、TBYTE_CTL和TBYTE_SRC

给MIG核用的,直接设置为“FALSE”

2.2.3 IO_FIFO

在7系列FPGA芯片,每个I/Obank都有IN_FIFO和OUT_FIFO,统称为IO_FIFO。尽管这些IO_FIFO是专门为内存应用设计的,但它们可以作为常规资源使用。对于一般用途,所有输入和输出均通过互连进行布线。IO_FIFO的最常见用途是与外部组件进行接口,作为IOLOGIC的扩展(例如ISERDES或IDDR和OSERDES或ODDR)。 由于它们具有通用的互连功能,因此IO_FIFO也可以用作其他结构FIFO资源。

每个I / O bank包含四个IO_FIFO,每个字节组一个IO_FIFO。 字节组被定义为存储体中的12个I / O。IO_FIFO在物理上与I / O字节组对齐。当使用IO_FIFO与IOI组件(例如输入和输出SERDES元素)进行接口时,这种对齐方式可产生最佳性能,这是它们的最常用用法。 但是,无论它们位于何处,IO_FIFO都可以与FPGA架构和其他I / O库中的资源接口(如下图所示,为方便阅读做了旋转)。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我