7系列selectio之ILOGIC

1整体介绍

如下图,ILOGIC位于IOB的旁边,它包含可边沿触发的D触发器、支持不同采样方式的IDDR、锁存器和组合逻辑用于对输入信号做特定处理。但ILOGIC并不是原语,不能被例化,我们可以使用它所包含的上述元素。

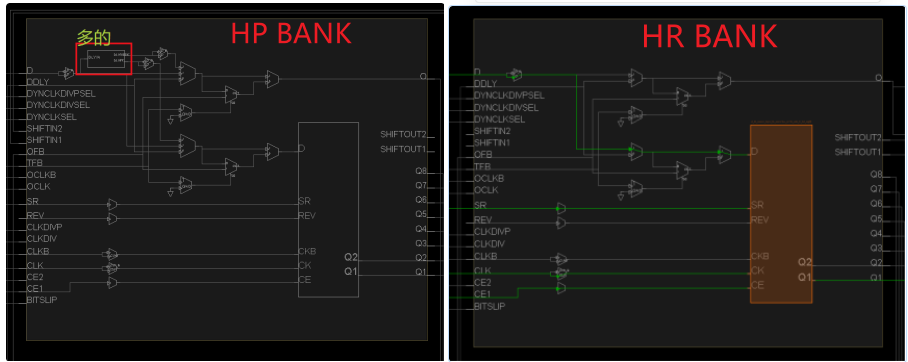

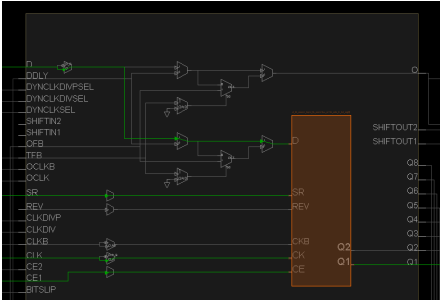

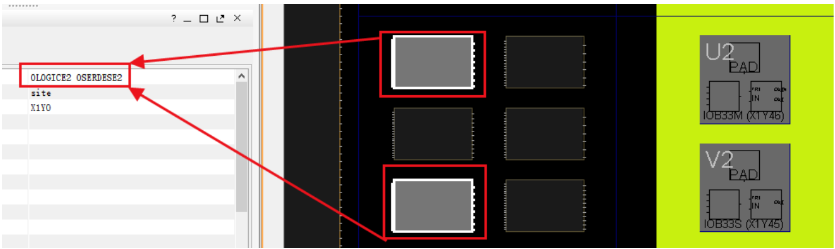

ILOGIC分为两种,一种是支持 HR BANK的ILOGIC2,一种是支持HP BANK的ILOGIC3。两者的区别在于ILOGIC3多了一个ZHOLD组件,如下图是device的截图,二者差别只在ZHOLD。

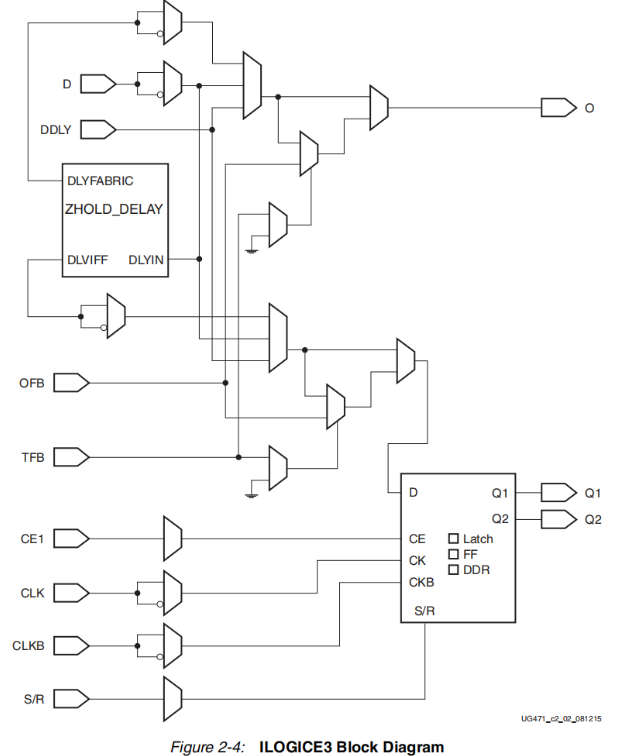

如下图HP BANK的ILOGIC3的逻辑示意图,ZHOLD全称是ZHOLD_DELAY,可以称之为零保持延迟。根据图片我们可以得知他是在D输入端,D输入端是连接到IOB的。ZHOLD可以自动与内部时钟(BUFG)延时匹配,使得pad-to-pad(引脚间)的保持时间为0,避免保持时间不满足。ZHOLD默认是使能的,如果时钟源来自MMCM、PLL,或者在Xilinx设计约束(XDC)中设置了IOBDELAY属性,那就不会自动启用了。

此外,ILOGIC的CE1是一个公共时钟使能信号,默认为高电平也就是有效的,当ILOGIC作为IDDR时我们可以使用它。

2.2支持功能

ILOGIC可以支持的具体操作如下:

1、边沿触发的D型触发器

这是固定在引脚旁边的触发器,离引脚位置固定且最近,可以保证信号到一级寄存器距离固定,有助于时序固定和采样固定,需要通过约束来使能这一操作:

set property IOB true [get ports {port name]]

如下图所示,就是使能IOB后将LOGIC作为了寄存器使用。

2、锁存器(S/R)

这也是xilinx触发器所具备的通用功能,可以实现同步或异步的置位和复位,也就是SR信号。

3、组合逻辑输入

就是输入信号直连到FPGA的逻辑资源,不会使用LOGIC的触发器,这个是软件自动使用的路径。例如点个灯,就采用的组合逻辑输出。

4、IDDR模式

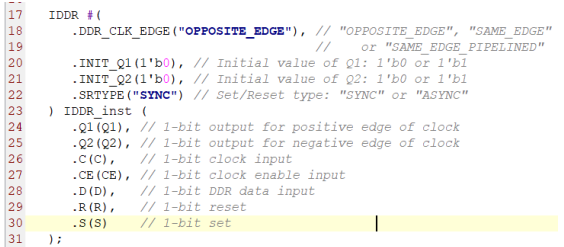

也就是双沿采样。支持的模式有主要有三种模块,分别为“OPPOSITE_EDGE”、“SAME_EDGE”和“SAME_EDGE_PIPELINED”。对应的原语如下,如果我们调用该原语即可实现双沿采样。

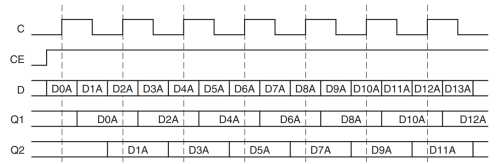

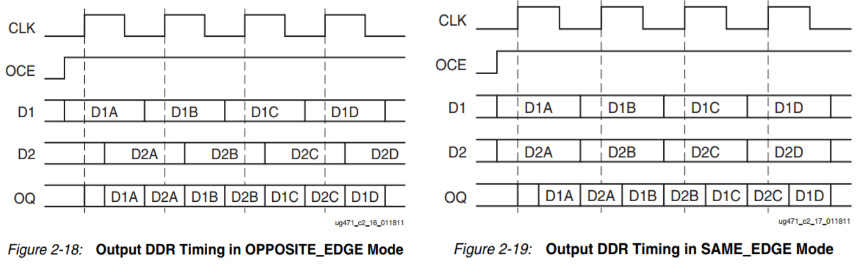

1、“OPPOSITE_EDGE”模式的时序图如下所示,上升沿下降沿均采样,并在即时期输出。输出相较于输入要延一拍

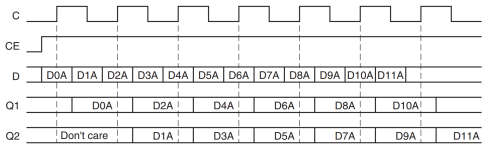

2、“SAME_EDGE”模式如下图所示,这种模式与模式1的差别在于数据对齐了。但错开了一位,这个才处理时需要额外注意

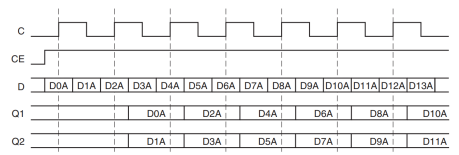

3、“SAME_EDGE_PIPELINED”是模式2的升级,我们发现更对齐了,DATA0和DATA1对齐。如果对时序要求不是那么苛刻,这倒是最友好的处理方法。

2.2.4 OLOGIC

如下图所示,每个IOB都有一个OLOGICE2,对于HP则是OLOGICE3。

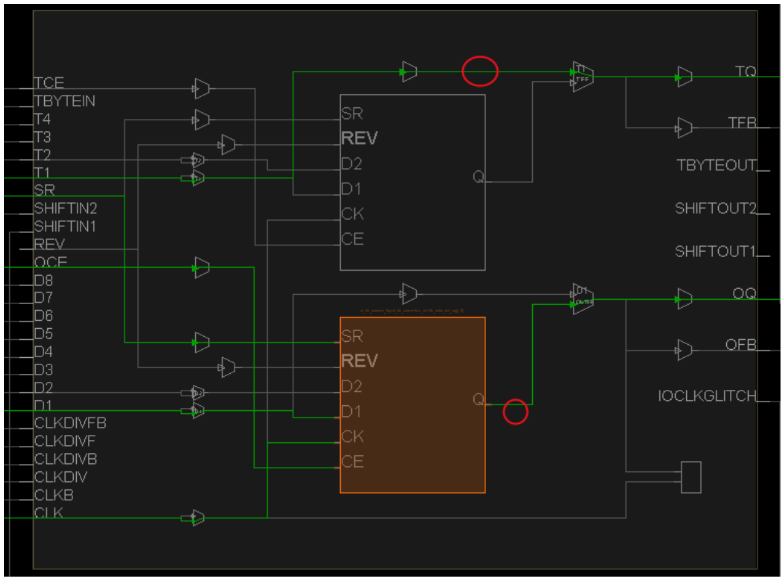

如下图可以看出OLOGIC的两条输出路径,一是经过触发器,另一是逻辑输出。

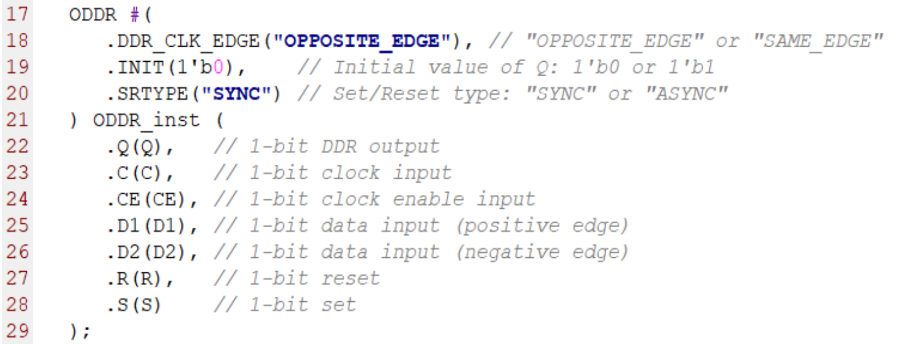

主要阐述下输出的DDR模式,这个与IOGICE2类似。原语如下:

DDR_CLK_EDGE:

可以选择"OPPOSITE_EDGE" 和"SAME_EDGE"

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我