7系列selectio之DCI概述

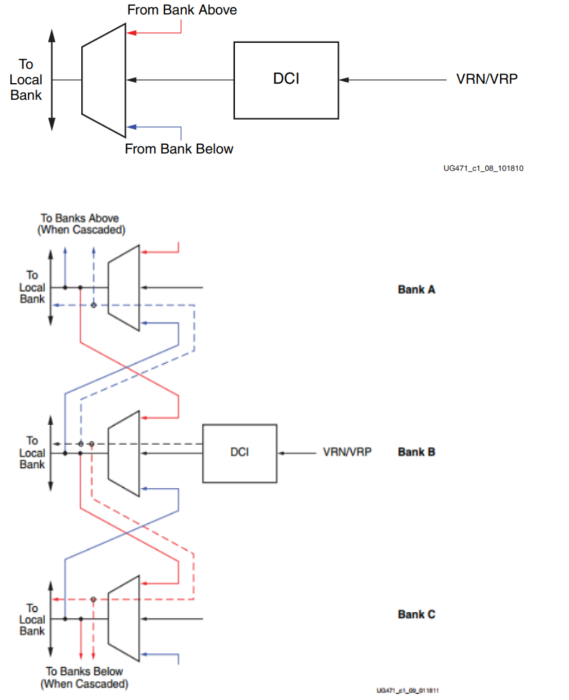

在上一章节介绍了阻抗及阻抗匹配的原理,在本章则介绍xilinx提供的阻抗匹配方法DCI技术,DCI(digitally controlled impedance )数字控制阻抗可以实现实时的阻抗调整和优化,并补偿因逻辑处理、温度和电压变化而引起的I/O阻抗变化而无需外接电阻。DCI技术仅在HP BANK支持,HR BANK不支持。支持DCI的每个BANK均有一对VRP/VRN管脚,这是一对多功能管脚,当启用DCI时,需要将VRN通过一个参考电阻上拉到Vcco,VRP通过一个参考电阻下拉到地。这两个管脚提供一个参考电压供DCI内部电路使用,DCI内部电路依据此参考电压调整IO输出阻抗与外部参考电阻匹配,此外,DCI还支持多个BANK级联以及模式设置。

每个BANK只有一组VRP/VRN管脚,改组BANK的所有引脚共享参考电阻阻值。

如果一列的多个bank使用相同参考阻值的DCI,在内部可以实现VRP/VRN的级联,形成master与slave的形式,在外部只需要对master BANK设置VRP/VRN即可,slave BANK悬空。

使用 DCI 级联时的指导原则如下:

DCI 级联只能用于HP BANK,因为HR BANK没有DCI.

主和从必须在同一列上

对于多个SLR的,不能跨dieDCI 级联不能通过采用堆叠硅互连 (SSI) 技术的较大 Virtex-7 器件的中介层边界。 这包括 XC7V2000T 和 XC7VX1140T 器件。

主和从必须具有相同的VCCO 和VREF(如果适用)电压。

同一 HP I/O 列中不使用 DCI(直通 bank)的 I/O bank 不必遵守 VCCO 和 VREF 电压规则来组合 DCI 设置。

所有主bank 和从 bank 都必须满足 DCI I/O bank 兼容性规则(例如,所有主库和从库只允许使用一种使用单一终端类型的 DCI I/O 标准)。

Xilinx 建议给未使用的 bank也上电,因为将未使用的 I/O bank 的 VCCO 管脚悬空会降低这些管脚和 bank 中的 I/O 管脚的 ESD 保护水平。 如果 bank 未上电,DCI 仍可通过未上电的 bank 级联。

阻抗匹配是在芯片执行启动序列期间进行的,在阻抗匹配未完成之前,DONE管脚是不会拉高的。当然,DCI校准可以通过实例化DCIRESET原语来重置,如下所示,将RST输入引脚拉高则会启动DCI的重新校准,当所有的DCI引脚校准完毕后LOCKED会拉高。该功能可应用于设备已经完成启动序列但温度或电压发生改变的情况。

DCIRESET DCIRESET_inst (

.LOCKED(LOCKED), // 1-bit output: LOCK status output

.RST(RST) // 1-bit input: Active-High asynchronous reset input

);

对于支持DCI控制阻抗驱动器的I/O标准,DCI可以将输出驱动程序配置为以下类型:

1、

对于支持并行端接的I/O标准,DCI可以创建一个戴维宁等效电路或分割电阻到VCCO的一半,

I/O标准命名约定添加了:

"DCI"是根据是否存在分割终端电阻来命名的,而不是根据其在引脚上的具体应用方式(输入、输出或双向)

如果只有在输出缓冲区处于三态(高阻态)时才存在分割终端电阻,那么"T_DCI"将出现在I/O标准的名称中。

Match_cycle

在DCI在DCI匹配之前要暂停的启动周期

DCIUpdateMode

DCIUpdateMode可以控制DCI电路对于阻抗匹配更新的行为。如下是该配置选项的可选约束行为,AsRequired是默认选项,表示DCI电路会根据需要自动更新,Continuous对于7系列等效于AsRequired,而Quiet为了灵活地控制DCI电路的阻抗匹配更新行为,根据具体的需求进行调整。例如,在某些应用中,可能需要频繁进行阻抗匹配更新以适应信号的变化,而在其他情况下,可能更希望DCI电路保持静默,不频繁地进行更新。

set_property BITSTREAM.CONFIG.DCIUPDATEMODE AsRequired [current_design]

set_property BITSTREAM.CONFIG.DCIUPDATEMODE Continuous [current_design]

set_property BITSTREAM.CONFIG.DCIUPDATEMODE Quiet [current_design]

总之,默认情况下为AsRequired,但在Xilinx实现软件中还提供了可选值Quiet,以满足不同应用场景下的要求。

DCIRESET原语

DCIRESET 是 Xilinx的原语,可以由它控制DCI控制器在代码运行阶段进行复位操作。但需要将 DCIUpdateMode 设置为 Quie。

应用场景:

如果 I/O bank 14 或 15(任何设备)或 bank 11、12、17、18、20 和 21(仅限 SSI 设备)中的任何多功能管脚被分配 DCI I /O 标准在用户设计中,DCIRESET 原语也应包含在设计中并使用。 应给DCIRESET的RST一个高脉冲,然后等待 LOCKED 信号被拉高,然后再使用所用的I/O。 这是必需操作,因为这些 I/O 会忽略在正常设备初始化期间发生的初始 DCI 校准。并且需要将 DCIUpdateMode设置为Quiet,如果不进行此操作则不无法作为DCI I/O标准使用,例如LVDCI_18会一直表现得好像处于高阻态,SSTL15_DCI会表现得好像没有内部终端电阻。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我