7系列selectio之DCI实现细节

DCI and 3-state DCI (T_DCI)

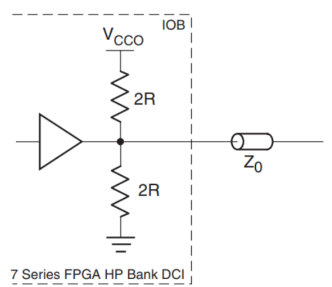

SSTL 和 HSTL I/O 标准的 I 类支持单向通信,也就说引脚或输入或输出,不能作为双向。 I 类 的SSTL 和 HSTL I/O 标准的 DCI 版本仅支持在输入端添加戴维南终端匹配。II 类 SSTL 和 HSTL I/O 标准支持单向和双向的通信,可以给它们的输入、输出或双向引脚均添加戴维南终端匹配。也就是如下图形式

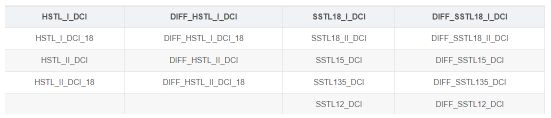

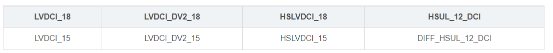

始终存在戴维南终端匹配的 I/O 标准下表所示。

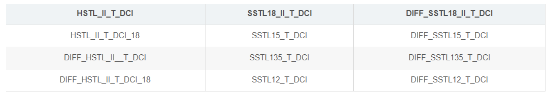

一般来讲,戴维南终端匹配应该始终存在于终端,也不再源端,然而有些场合需要关闭并联终端阻抗,例如三态,用T_DCI表示,带有T_DCI的说明这个IO是支持双向传输,当作为输出缓冲区则需要关闭终端阻抗,当处于输入或空闲则需要打开终端阻抗。

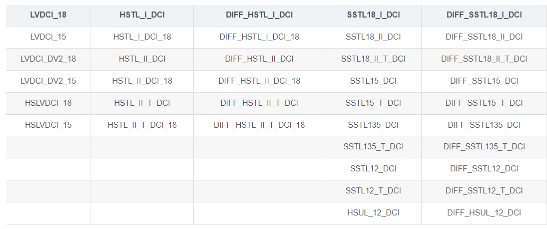

所有 7 系列设备 DCI I/O 标准:

要在 7 系列器件中正确使用 DCI:

VCCO 管脚必须根据该 I/O bank 中的 IOSTANDARD 连接到适当的 VCCO 电压。

必须在软件中使用正确的 DCI I/O BUF,方法是使用 IOSTANDARD 属性或 HDL 代码中的实例化。

DCI 标准要求将外部参考电阻器连接到多用途引脚(VRN 和 VRP)。 需要时,这两个多用途管脚不能用作使用 DCI 的 I/O bank 中的通用 I/O,或级联 DCI 时的主 I/O bank 中的通用 I/O。引脚 VRN 必须通过其参考电阻上拉至 VCCO。 引脚 VRP 必须通过其参考电阻下拉至地。 在从 I/O bank 中级联 DCI 时,此要求有一个例外,因为 VRN 和 VRP 引脚可用作通用 I/O。

具有受控阻抗驱动器的 DCI 标准可用于仅输入信号。 对于这种情况,如果这些引脚是给定 I/O bank 中唯一使用 DCI 标准的引脚,则该 bank 不需要将外部参考电阻器连接到 VRP/VRN 引脚。 当这些基于 DCI 的 I/O 标准是 bank 中唯一的标准时,该 bank 中的 VRP 和 VRN 管脚可用作通用 I/O。

VRP/VRN 上不需要参考电阻的 DCI 输入如下表所示。

应选择外部参考电阻器的值,以提供所需的输出驱动器阻抗或分路终端阻抗。 例如,当使用 LVDCI_15 时,要实现 50Ω 的输出驱动器阻抗,VRN 和 VRP 引脚上使用的外部参考电阻应各为 50Ω。 使用 SSTL15_T_DCI 时,要实现 50Ω Thevenin 等效端接 ® 到 VCCO/2,外部参考电阻应为 100Ω,即 (2R)。 Xilinx 要求在 VRP 和 VRN 引脚上使用完全相同的电阻值,以实现预期的 DCI 行为。

遵循 DCI I/O Bank规则:

使用 DCI 级联时,VREF 必须与同一 I/O bank 或一组 I/O bank 中的所有输入兼容。

VCCO 必须与同一 I/O bank 中的所有输入和输出兼容。

分离端接、受控阻抗驱动器和具有半阻抗的受控阻抗驱动器可以共存于同一组中。

HR I/O Bank 中未校准的拆分终端 (IN_TERM)

HR I/O bank 有一个可选的片上分离终端特性,与 HP I/O bank 中的三态分离终端 DCI 特性非常相似。 与 HP 组中的三态分离端接 DCI 类似,HR 组中的选项使用两个目标电阻值两倍的内部电阻器创建戴维南等效电路。 一个电阻端接至 VCCO,另一个端接至地,为中点 VCCO/2 提供戴维南等效端接电路。 当输出缓冲器为三态时,输入端和双向引脚上始终存在端接。 然而,这种未经校准的分离式终端选项和三态分离式终端 DCI 之间的一个重要区别是,在使用 DCI 时,该功能不是校准到 VRN 和 VRP 引脚上的外部参考电阻,而是调用没有校准例程的内部电阻来校准补偿温度、过程或电压变化。 此选项的目标戴维南等效电阻值为 40Ω、50Ω 和 60Ω。

与 DCI 终端的另一个区别是如何在设计中调用这种未经校准的终端。 虽然通过将 T_DCI I/O 标准分配给 HP I/O bank 中的 I/O 管脚来调用三态分离终端 DCI 选项,但通过将 IN_TERM 约束分配给 I/O 管脚来调用未校准的分离终端选项 HR I/O bank 中的网络。这可以通过多种方式完成,包括在源 HDL 设计中、在 UCF、NCF 或 XCF 文件中,或在 PlanAhead软件中。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我