7系列selectio之DCI的实现

阻抗匹配的方法有很多种,Xilinx大致提供了两种匹配方法,即源端串联阻抗匹配和终端阻抗匹配,终端阻抗匹配又分为上拉单电阻形式和戴维南终端匹配,分别用于支持不同的I/O标准,下面就分别介绍:

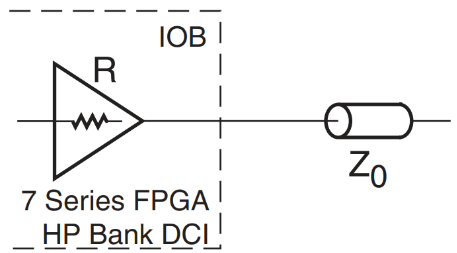

1串联终端匹配:

如下图所示,源端串联匹配需配置VRN/VRP 管脚参考电阻为Z0大小,即R=Z0,由于输入端为高阻抗,近乎理解为开路,那么串联分压,驱动信号传播时以其幅度的50%向负载端传播。反射系数=(Z0-Z1)/(Z0+Z1),反射系数接近+1,信号到输入端如同撞墙,因此反射信号都会反射回来。反射信号与源端传播的信号叠加,使负载端接受到的信号与原始信号的幅度近似相同;负载端反射信号向源端传播,到达源端后被匹配电阻吸收;反射信号到达源端后,源端驱动电流降为0,直到下一次信号传输。

相对并联匹配来说,串联匹配不要求信号驱动器具有很大的电流驱动能力。

选择串联终端匹配电阻值的原则很简单,就是要求匹配电阻值与驱动器的输出阻抗之和与传输线的特征阻抗相等。理想的信号驱动器的输出阻抗为零,实际的驱动器总是有比较小的输出阻抗,而且在信号的电平发生变化时,输出阻抗可能不同。比如电源电压为+4.5V的CMOS驱动器,在低电平时典型的输出阻抗为37Ω,在高电平时典型的输出阻抗为45Ω[4];TTL驱动器和CMOS驱动一样,其输出阻抗会随信号的电平大小变化而变化。因此,对TTL或CMOS电路来说,不可能有十分正确的匹配电阻,只能折中考虑。

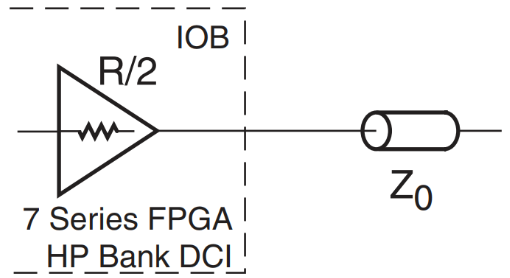

DCI 还为驱动器提供了一半的参考电阻器阻抗。 参考电阻值翻倍可将这些电阻的静态功耗降低一半。 支持具有半阻抗的受控阻抗驱动器的 DCI I/O 标准是 LVDCI_DV2_15 和 LVDCI_DV2_18。

下图说明了一个 7 系列器件内部具有半阻抗的受控驱动器。 参考电阻 R 必须为 2 × Z0 以匹配 Z0 的阻抗。

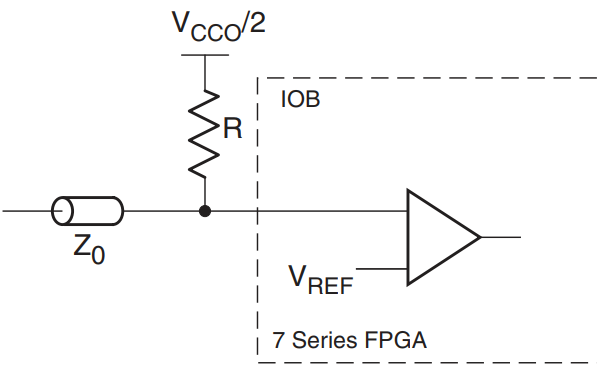

2并联终端匹配

并联终端匹配的理论出发点是在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。实现形式分为单电阻和双电阻两种形式。

并联终端匹配后的信号传输具有以下特点:

A驱动信号近似以满幅度沿传输线传播;

B所有的反射都被匹配电阻吸收;

C负载端接受到的信号幅度与源端发送的信号幅度近似相同。

单带你组形式:

在实际的电路系统中,芯片的输入阻抗很高,因此对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等。假定传输线的特征阻抗为50Ω,则R值为50Ω。如果信号的高电平为5V,则信号的静态电流将达到100mA。由于典型的TTL或CMOS电路的驱动能力很小,这种单电阻的并联匹配方式很少出现在这些电路中。

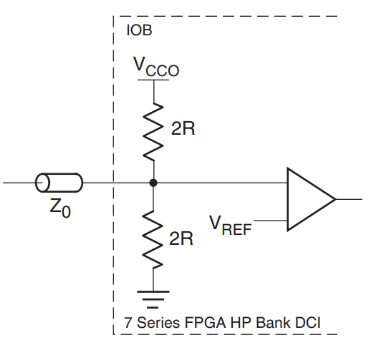

双电阻形式:

双电阻形式的并联匹配,也被称作戴维南终端匹配,要求的电流驱动能力比单电阻形式小。这是因为两电阻的并联值与传输线的特征阻抗相匹配,每个电阻都比传输线的特征阻抗大。考虑到芯片的驱动能力,两个电阻值的选择必须遵循三个原则:

⑴.两电阻的并联值与传输线的特征阻抗相等;

⑵.与电源连接的电阻值不能太小,以免信号为低电平时驱动电流过大;

⑶.与地连接的电阻值不能太小,以免信号为高电平时驱动电流过大。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我