7系列selectio之ISERDESE2

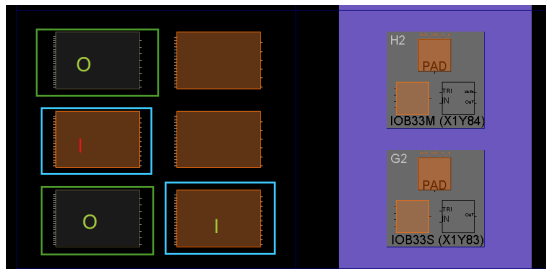

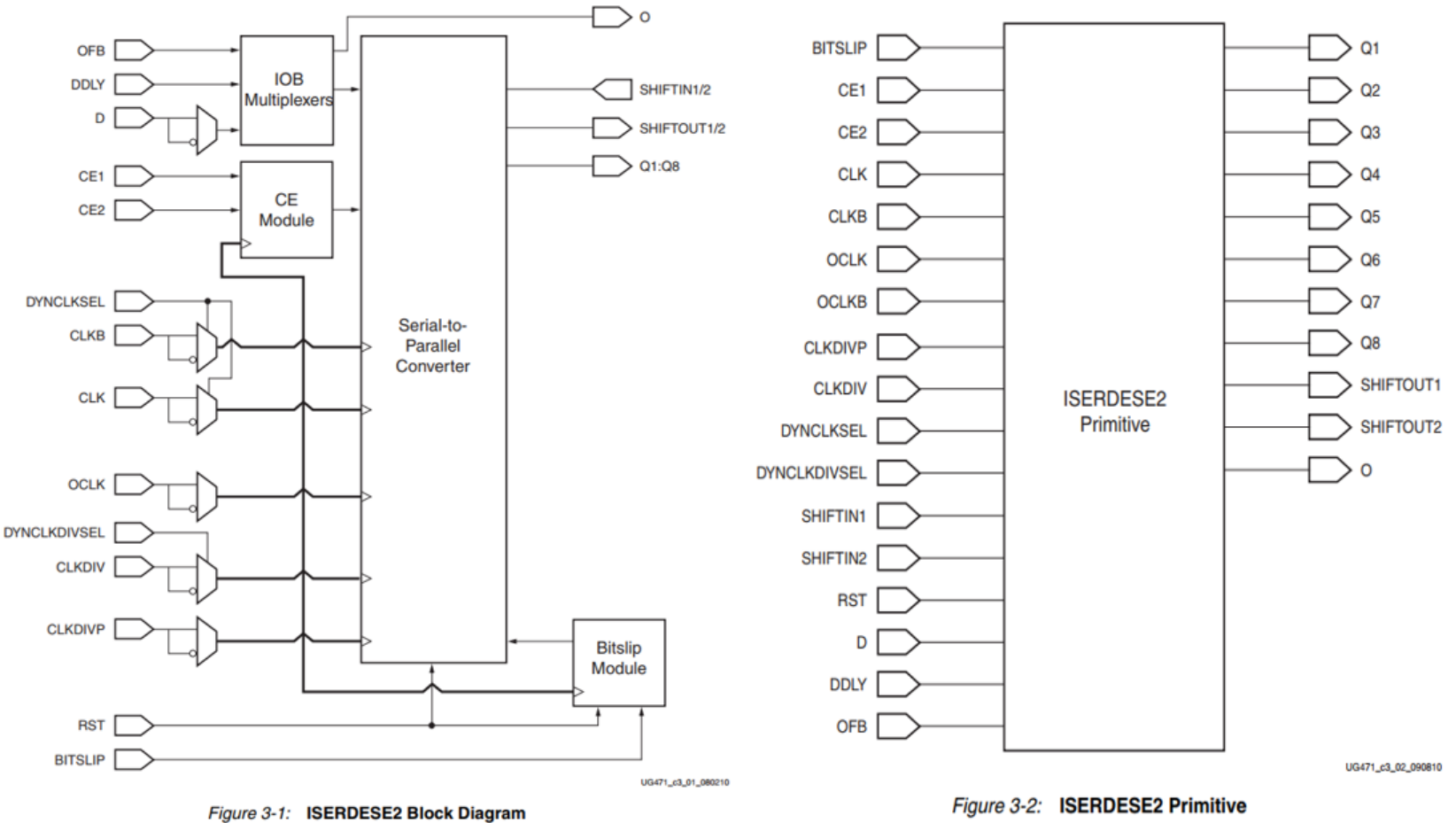

如下图所示,每组引脚都有两个OSERDESE2和ISERDESE2。可以实现串行与并行之间的转换,每个SERDES都支持串行与8bit并行之间的转换。并可以通过Bitslip实现数据的重新对齐。

1 ISERDESE2

ISERDESE2主要是串行输入,可根据对ISERDESE2的模式配置,实现不同模式。如下图是ISERDESE2的例化,可以在vivado的原语里面搜索到该模块。

首先先看下参数的配置,具体解释如下表

第一部分:模块参数

参数部分的设置或是调用原语的设置或是使用相应IP核的配置。

1、DATA_RATE

是用于对串行数据采样时的采样模式设置,有SDR和DDR两种模式设置,SDR(single data rate)是单沿采样,DDR(double data rate)是双沿采样,该模块默认为DDR模式。

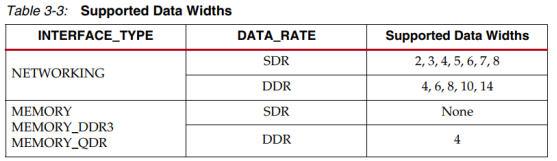

2、DATA_WIDTH

是设置串并转换的位宽,每一个“ISERDESE2”可以实现8bit位宽的输出,但通过不同的模式设置就有了多种位宽输出格式,具体如下表所示。其中“NETWORKING”类型的DDR模式可支持最大14bit位宽,这时就需要将两个“ISERDESE2”采用主从模式进行串联实现。具体方式会放在下文阐述。

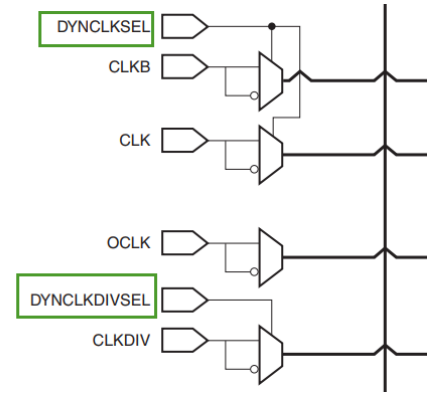

3、DYN_CLKDIV_INV_EN和DYN_CLK_INV_EN

如下图所示,在“ISERDESE2”接口有“DYNCLKDIVSEL”和“DYNCLKSEL”两个信号分别控制“CLKDIV”和“CLK”是否进行取反操作。而“DYN_CLKDIV_INV_EN”和“DYN_CLK_INV_EN”就是“DYNCLKDIVSEL”和“DYNCLKSEL”这两个选择信号的的使能信号,只有在“DYN_CLKDIV_INV_EN”和“DYN_CLK_INV_EN”为“TURE”的情况下,才能进行选择,默认是“FALSE”。而这种操作只支持“MEMORY_QDR”和“MEMORY_DDR3”模式,一般用不到。

4、INTERFACE_TYPE

这是模式设置,“ISERDESE2”支持内存模式、网络模式以及过采样模式。内存模式即MEMORY模式、MEMORY_DDR3模式和MEMORY_QDR模式。例如我们用“mig_7series_0”核就是MEMORY_DDR3模式,另外还支持 OVERSAMPLE和 NETWORKING模式。NETWORKING模式就是实现串并转换,OVERSAMPLE是同频多相位采样模式,可实现与数据同频的时钟对数据采样。当然,这还需要其它逻辑的配合,这个在《xapp523》中有详细的介绍。

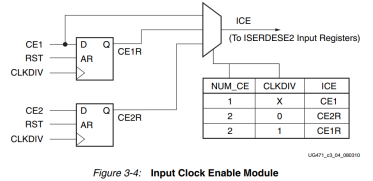

5、NUM_CE

它的值可以是1也可以是2,表示的是接口信号(CE1 and CE2)的使能个数。默认是2,具体CE1和CE2在接口信号相关部分阐述。

6、OFB_USED

这和“OLOGICE2/3”有关。

7、SERDES_MODE

主从模式设置,SERDES_MODE属性定义使用宽度扩展时ISERDESE2模块是主模块还是从模块,用于扩展连接,例如14bit位宽的使用。

8、INIT_Q1~Q4

设置第一个采样寄存器的初始值,在OVERSAMPLE模式时用于初始化采样值。

9、SRVAL_Q1~Q4

设置第二个采样寄存器复位后的值,默认即可。

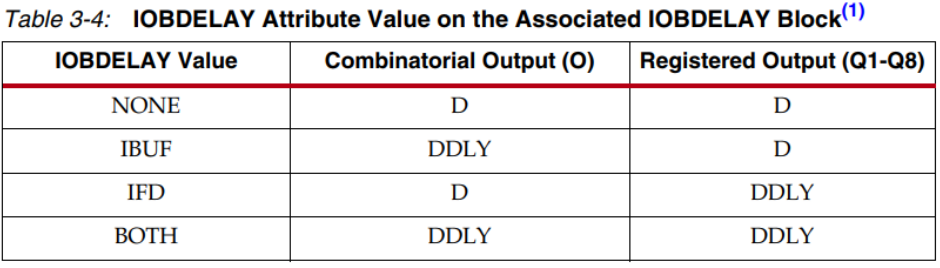

10、IOBDELAY

D和DDLY引脚是ISERDESE2的专用输入。D输入是与IOB的直接连接。DDLY引脚是与IDELAYE2的直接连接。这使用户可以拥有已注册(Q1-Q8)或组合路径(O)输出的延迟或非延迟版本的输入。IOBDELAY属性确定应用于ISERDESE2的输入。表3-4显示了同时连接D和DDLY时IOBDELAY值的每种设置的结果。最后注释了依据当D和DDLY都接入ISERDESE2时的选择,那么是不是如果只接一个可以自动识别?

第二部分:接口信号

如下图所示,是ISERDESE2模块的接口信号,接下来就对此进行逐个分析。

1、Q1 – Q8

ISERDESE2模块转并后的输出端口,可实现最多8bit的输出,如果使用DDR模式,可扩展为两个ISERDESE2模块,实现10、14bit的输出。输出位宽是根据参数进行配置。

2、O

是D或者DDLY输入的直接输出

3、FTOUT1、SHIFTOUT2和SHIFTIN1、SHIFTIN2

是用于ISERDESE2模块的扩展功能的。

4、D

IOB的输入信号,当然也可以不是来自IOB

5、DDLY

也是串行输入信号,但是从IDELAYE2模块来的。

6、CLK

用于串行数据的时钟输入

7、CLKB

用于QDR模式的。咱们用不到,当使用MIG核时会用到。

8、CLKDIV

并行数据的输入时钟,例如8-1模式,SDR模式,并行时钟100MHz,串行时钟12.5Mhz。

9、CLKDIVP

仅通过MIG工具支持。 由PHASER_IN划分为MEMORY_DDR3模式下的CLK。 所有其他模式都接地

10、OCLK

时钟输入信号,NETWORKING模式是用不到的,在其他模式用于时钟输入,例如OVERSAMPLE模式

11、RST

高有效的复位信号,置位后,复位输入将导致CLK和CLKDIV域中大多数数据触发器的输出被异步驱动为低电平

12、CE1和CE2(待补充)

每个ISERDESE2模块都包含一个输入时钟使能模块

13、BITSLIP

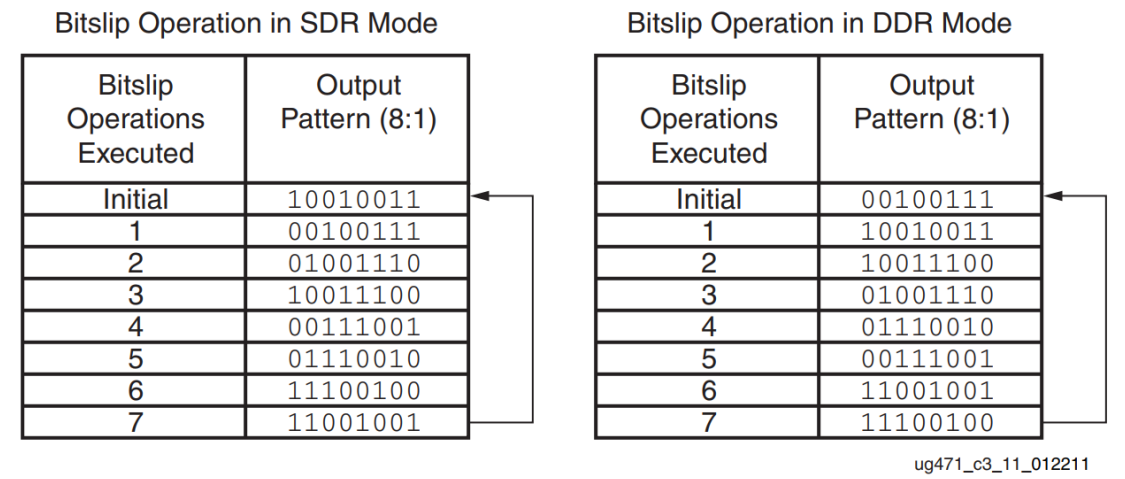

通过对BITSLIP引脚置位可以实现并行端口的字节对齐。只能在NETWORKING模式下使用。一般我们使用K码,例如K28.5实现字节对齐,就是在并行接口寻找到K28.5,寻找方式是位滑入。《ug471》也指出看似如同桶型位移操作其实并非如此,而是如同流水线般,在数据流中找到训练码,并以此来确定串并转换的起始位,如下图所示。

对于SDR模式和DDR模式,滑入还是有区别的,SDR模式每次移入1bit,DDR模式每次移入1bit或3bit,是交替的。

另外,BITSLIP的是在CLKDIV时钟下,每一个时钟周期实现一位的滑入,两次滑入之间需将BITSLIP拉低,并且,在BITSLIP置一的两个周期,对于DDR是三个周期之后才是滑入之后的值。

14、OFB

串行输入数据端口(OFB)是ISERDESE2的串行(高速)数据输入端口。 该端口仅可与7系列FPGA OSERDESE2端口OFB一起使用。当属性OFB_USED = TRUE时,启用此功能

15、DYNCLKDIVSEL和DYNCLKSEL

动态时钟反相引脚DYNCLKSEL和DYNCLKDIVSEL分别与DYN_CLK_SEL_EN和DYN_CLKDIV_SEL_EN结合使用时,可使用户动态切换相应时钟源的极性。此操作将导致进入ISERDESE2的时钟异步切换,并有可能导致ISERDESE2产生错误的数据,直到将ISERDESE2复位为止。 仅在MEMORY_QDR和MEMORY_DDR3模式下支持此操作。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我