管理接口状态机分析(一)

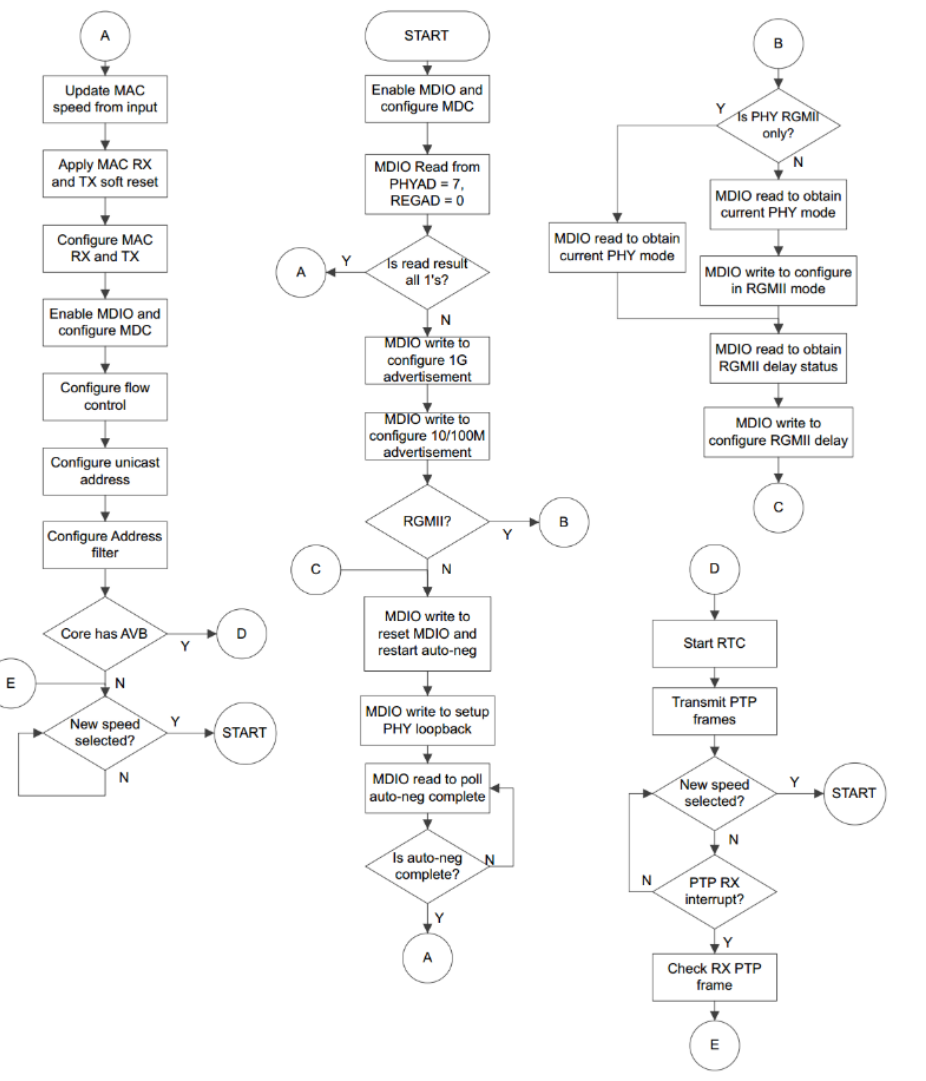

如下是管理接口状态机,接下来我们对此进行详细的分析

这个模块有三个状态机。

1、axi_state:

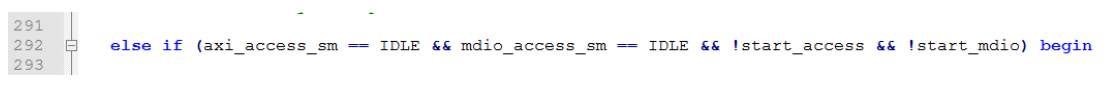

控制该模块配置管理的整个进程,可以说是指导操作步骤,是主动工作的,这个状态机执行的首要条件是两个“从状态机”在IDLE状态,且没有启动相关进程。

由下图可知“start_access”信号启动“axi_access_sm”状态机,“start_mdio”信号启动“mdio_access_sm”状态机。

这里的设计思想是:

“axi_state”状态机控制进程,到了一个新的进程,将“start_access”或“start_mdio”拉高,让另外两个模块执行具体的操作。由于这两个信号拉高,“if”条件不满足,跳出该状态机锁存状态。等相对应状态机执行完成后有满足了条件继续下一个进程。

2、mdio_access_sm:

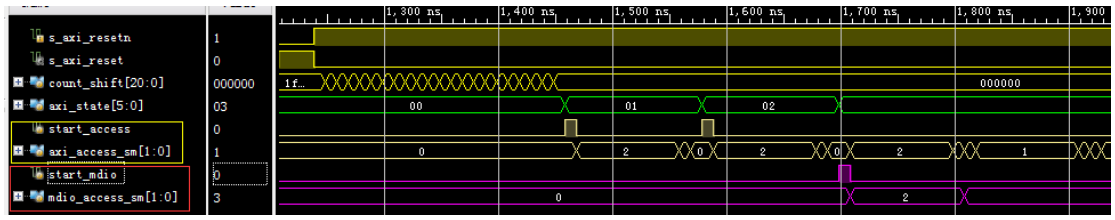

“axi_state”状态机进程中有些数据是对核的配置,有些是对PHY芯片配置寄存器操作的。这个状态机主要是描述对PHY芯片操作的相关逻辑。是由“start_mdio”启动的。具体的读写数据还是由“axi_access_sm”状态机完成,本状态机主要是做发送数据的组合。状态机的执行有个限制条件,如下图,所以该状态机和“axi_state”一样,执行一个周期锁存了,等待数据或读或写完成后再根据条件来启动。

3、axi_access_sm:

该状态机是控制aix4_lite接口的读写操作,无论是对核配置还是对PHY芯片的寄存器读写,都是根据这个状态机来完成的。

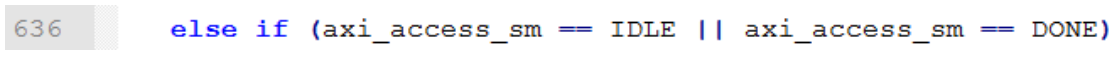

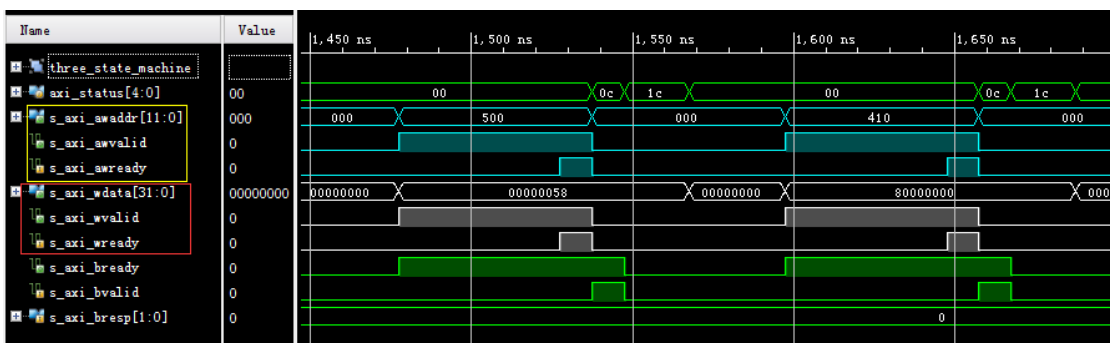

写操作时序如下图所示:

“axi_status[2]”表示写数据操作,“axi_status[3]”表示写地址操作,均是收到从器件响应完成对应操作置一,“axi_status[4]”置一表示收到本次写数据完成标识。这2bit为1表示一次写完成。该状态机回到IDLE状态。

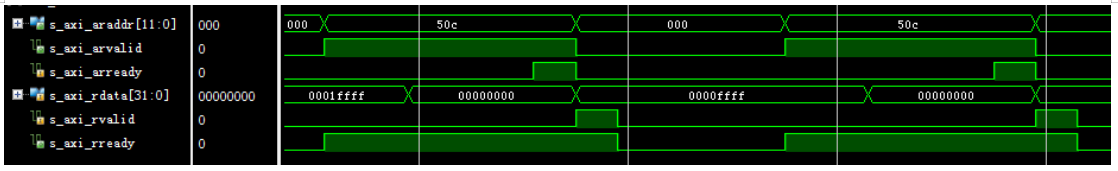

读操作时序如下图所示:

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我