基于PI的CDR

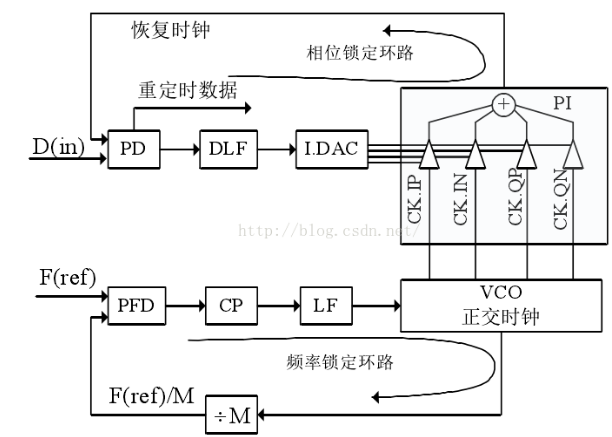

下面来简单介绍基于 PI 的 CDR 电路,一个基于相位插值的 CDR 拓扑结构如图所示。与图 (a)的 CDR 相比,在相位锁定环路中没有CP (Charge pump,电荷泵)和 LP 单元,取而代之的是数字低通滤波器(Digital Low-passFilter,DLF)和电流型数字-模拟转换器(Digital Analog Converter,DAC),而 VCO 由 PI 替代。I.DAC 通过对 PI的直接控制,使 PI 输出的时钟相位产生变化。这种结构的 CDR 与基于 PLL 的 CDR相比,具有环路稳定性增强、捕获时间缩短,并且无抖动峰值的优点,但需要注意的是抖动峰值的消除仅适用于当环路延时与 PI 相位的更新时间相比不是很大的时候。

鉴频鉴相器(Phase Frequency Detector,PFD)

基于 PI 的 CDR 的另外一个优点是能够在源异步方式中,在允许的发送器和接收器频率偏移条件下,可以在很宽的数据率范围内工作。设计基于 PI 的 CDR时,主要考虑的方面是 I.DAC 的精度,PI 的线性度和环路延时,因为这些因素会对 CDR 的抖动性能有直接影响。

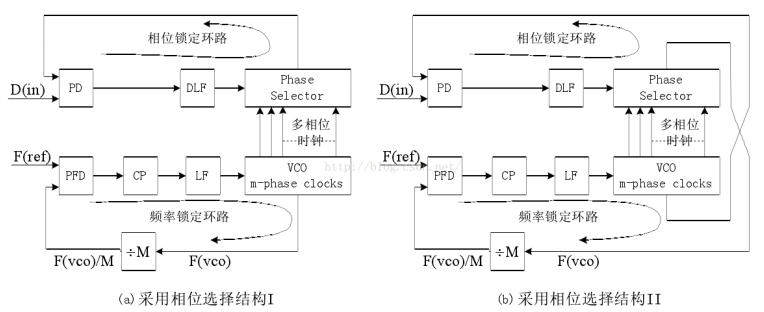

图为 PI 的CDR结构的两种变化形式,采用一个相位选择器替换了图 2-10中的 I.DAC 和 PI。两种结构的共同优点是可以采用更少的模拟电路,因而设计面积更小。图 2-11(a)结构的优点是采用独立的相位和频率锁定环路,降低了环路带宽稳定性的要求,另外在相位跟踪环路中采用数字电路实现方式,降低了工艺、电源电压、温度变化对系统性能的影响。该结构主要的缺点是数字控制时钟相位切换时,将会导致比较大的 cycle-to-cycle 抖动,而且当采用更多级的 VCO 以得到较小间隔的相位时钟时,会使 VCO 的振荡频率降低而功耗增加,版图面积也相应地增大。一种减小由相位切换导致的抖动的方法是,将相位选择输出和 VCO 输出交换,如图 2-11(b)所示,这样使得在相位锁定环路中,经 DLF 的输出信号控制得到的时钟信号的相位跳变,经过频率锁定环路中的 CP 和 LF 的低通滤波变得平缓了,但是这种结构将会导致多通道间不能够再共享同一个参考时钟的频率锁定环路。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我