发送模块介绍(一)

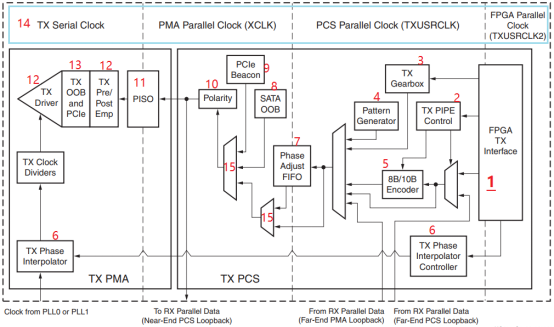

如下图所示,我们可以将其分为两个部分,即PCS和PMA。在本章会对每个模块进行大致的介绍,了解其功能,接下来章节会对用到的模块进行详细阐述,而这些模块也是我们实现高速串行接口的核心。

1、 FPGA TX Interface

就是用户数据的输入接口,也就是上述的

2、 TX PIPE Control

PIPE的全称是Physical Interface for PCI Express,即PCIe物理层接口,如果使能了PCIE接口,则该通道是PCIE的数据通道。

3、 TX Gearbox

GTP除了支持8B / 10B编码外还支持64B / 66B和64B / 67B编码方式,以此来提高有效数据的传输效率,支持这些通过对该模块的配置实现。

4、 Pattern Generator

伪随机序列(Pseudo-random bit sequences,PRBS)是一种貌似随机,实际上是有规律的周期性二进制序列,用于高速串行通信通道传输的误码率测试。

5、 8B/10B Encoder

8B/10B 编码是非常重要的一个知识点。位宽8bit可以组织出 256种数据,位宽10bit可以组织出1024种数据,我们就从这1024种数据中挑出一些0和1的个数应尽量相等的数据来表示8bit数据,另外还可以再挑出12种控制字符,来表示链路的状态或者控制信息,这不仅可以保持良好的直流平衡,增加了数据的传输距离,提供了更为有效的错误检测机制,还可以用来实现时钟修正、块同步、通道绑定和将带宽划分到子信道等

6、 TX Phase Interpolator Controller

这是TX相位插值器控制器模块,支持动态控制TX相位插值器(TX PI),TX PMA中的数据进行微调。

7、 Phase Adjust FIFO

为了保证数据传输速率一致,XCLK必须和TXUSERCLK时钟的速率匹配,并且要解决2个时钟域之间的相位差异。利用TX BUFFER介于XCLK和TXUSERCLK俩时钟域之间,用于匹配两者的速率和相位偏差。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我