1.5 selectio之I/O标准和终端技术(四)

Xilinx参照JEDEC,支持了许多I/O标准,例如LVTTL、LVCMOS、LVDCI、HSTL、SSTL、HSUL、LVDS等等,本文主要描述LVDCI和HSTL相关内容。

1SSTL

SSTL(Stub-Series Terminated Logic)是一种主要用于DDR2DDR3等内存相关接口的I/O标准,支持SSTL18(1.8V)、SSTL15(1.5V)、SSTL135(1.35V)和SSTL12(1.2V),分别支持DDR2 SDRAM、DDR3 SDRAM、DDR3L SDRAM和RLDRAM3。

Xilinx对这四种I/O标准的支持大体相似,可分单端单向、单端双向、差分单向和差分双向通信。但不同的电平包含的I/O标准却也不尽相同。下面从三个方面介绍SSTL

1是SSTL不同幅值所包含的I/O标准类型以及应用场景

2是同一类型的电路设计,例如SSTL18、 SSTL15、 SSTL135 和 SSTL12 ,随是不同幅值但电路是一样的3是不同I/O标准支持的原语及属性的配置

1.1 SSTL分类

下面分别介绍一下SSTL这个标准包括包括哪些?

1.1.1 SSTL18

SSTL18 由 JEDEC 标准 JESD8-15定义的用于 DDR2 SDRAM 接口。分为1类和II类两种标准,I类标准可以减少过冲进而提升信号质量,其实对于xilinx来说,两者的电路时一致的。

1、I类包括的电平标准:SSTL18_I、DIFF_SSTL18_I、SSTL18_I_DCI、DIFF_SSTL18_I_DCI、

2、II类包括的电平标准:SSTL18_II、DIFF_SSTL18_II

1.1.2 SSTL15

SSTL15 由 JEDEC标准ESD79-3E粗略定义的用于DDR3 SDRAM 接口。HR和HP BANK均支持,当然包括DCI的只有HP BANK支持,但这里有两个”_R“的I/O 标准,这是一个仅HR BANK支持且驱动能力减弱的IO标准,目的是减少信号的过冲进而保证完整性。

1、 SSTL15_R、 DIFF_SSTL15_R

2、SSTL15、IFF_SSTL15、SSTL15_DCI、 DIFF_SSTL15_DCI、

1.1.3 SSTL135

SSTL15 由 JEDEC标准JESD79-3-1粗略定义的用于DDR3L SDRAM 接口,与SSTL15类似,就不赘述了。

1、SSTL135_R、DIFF_SSTL135_R 、

2、SSTL135、SSTL135_DCI、DIFF_SSTL135 、DIFF_SSTL135_DCI

1.1.4 SSTL12

SSTL12 支持 Micron 的下一代 RLDRAM3 存储器,仅HP BANK支持。

SSTL12、SSTL12_DCI 、DIFF_SSTL12和DIFF_SSTL12_DCI

1.2 电路设计

1.2.1 单端IO

这里描述的是单端IO的电路实现方案,包括单端单项、单端双向以及是否包含DCI四类。

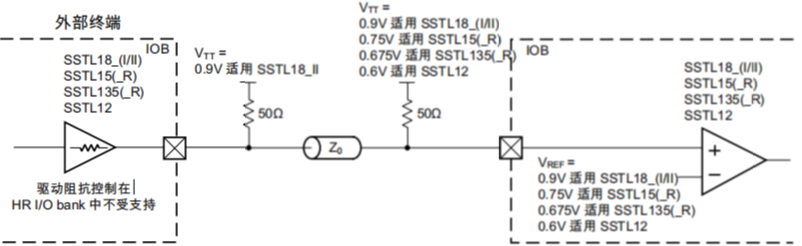

如下是单端单项且不包含DCI的,一共7个IO标准,采用外部的单端上拉来做阻抗匹配,在接收端采用单端输入差分接收的方式接收数据,接收的N端就是所连BANK的参控电压,为VCCO的一半。对于SSTL

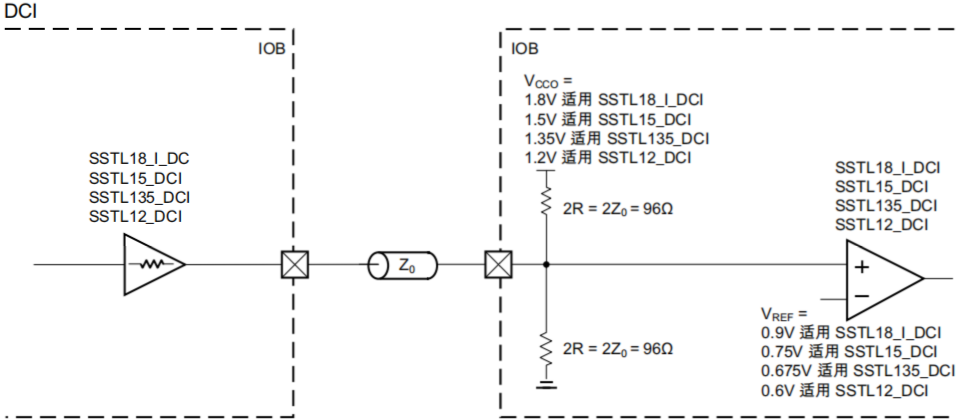

如下是包含DCI的单端连接电路,

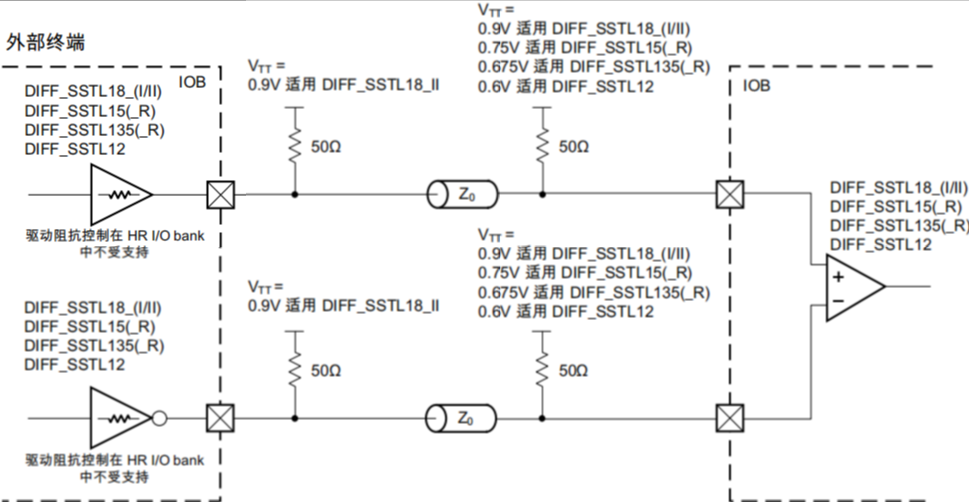

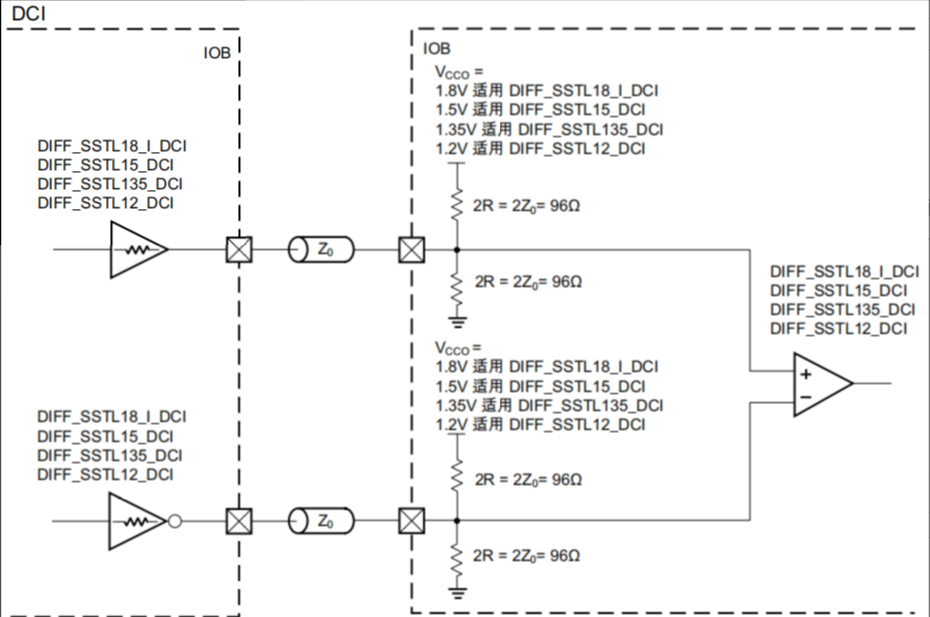

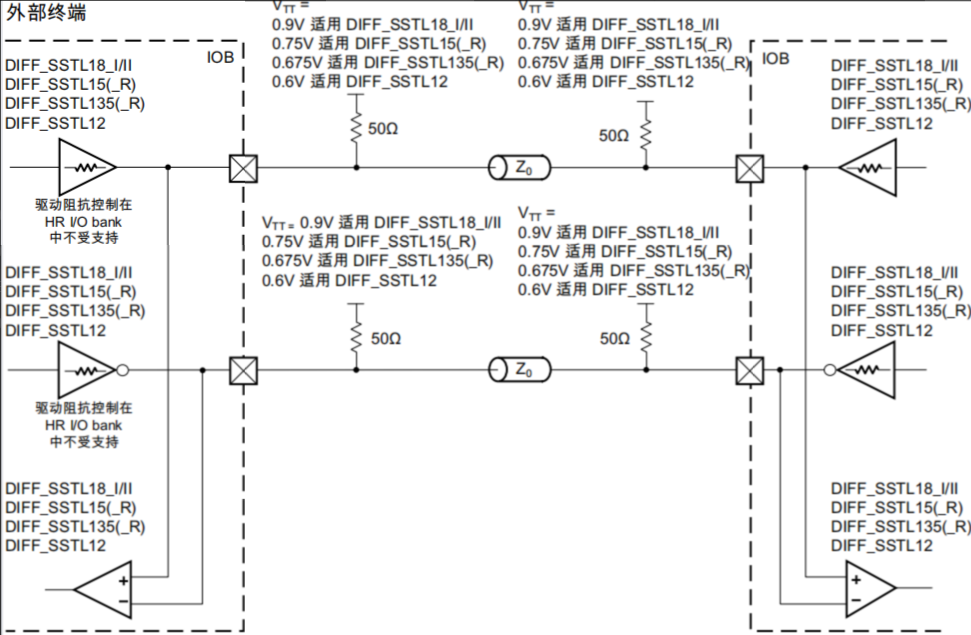

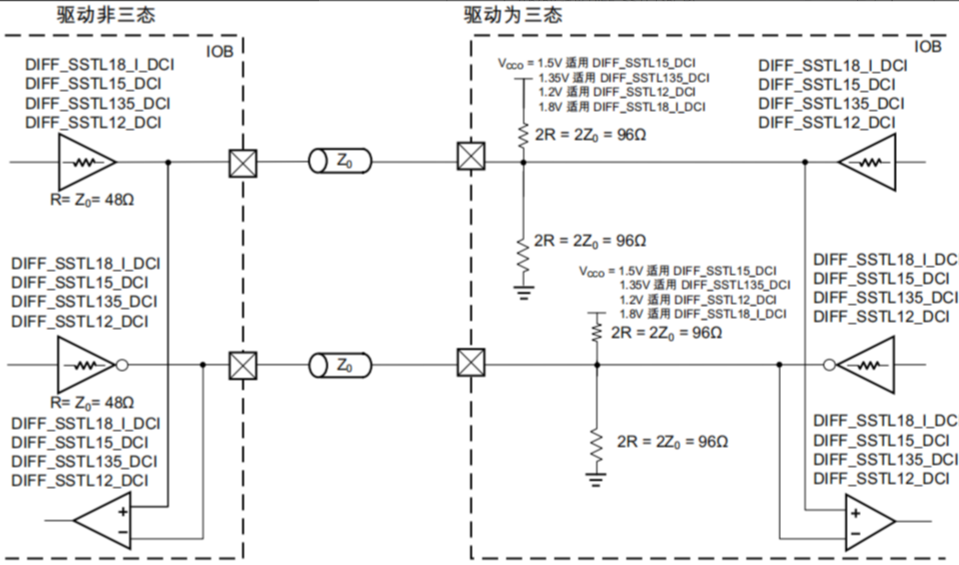

1.2.2 差分IO

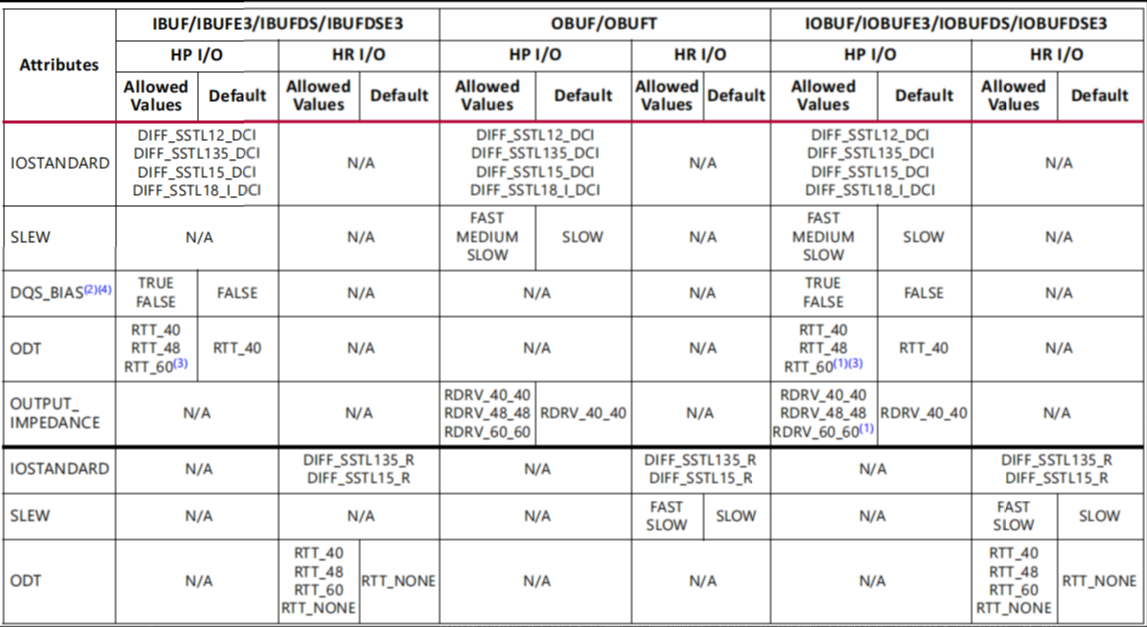

1.3 原语

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我