1.3 selectio之I/O标准和终端技术(二)

本章节是介绍Xilinx ultraScale系列FPGA所支持的I/O 标准的第二部分,将介绍LVDCI、HSTL和SSTL这三种IO标准,关于I/O 标准的介绍可参考XX、

1.1LVDCI

LVDCI标准仅HP BANK支持,某些I/O标准(例如LVCMOS)必须保证源的驱动阻抗与线路的特征阻抗匹配,所以就需要对驱动源做阻抗匹配,Xilinx提供了DCI帮我们轻松的实现了源阻抗匹配,不要外接匹配电阻。这种电平标准信号是对输出信号的阻抗进行控制和调整,使得输出信号具有受控和稳定的阻抗特性,以适应特定的传输线或系统要求,进而提高信号的传输质量和完整性。

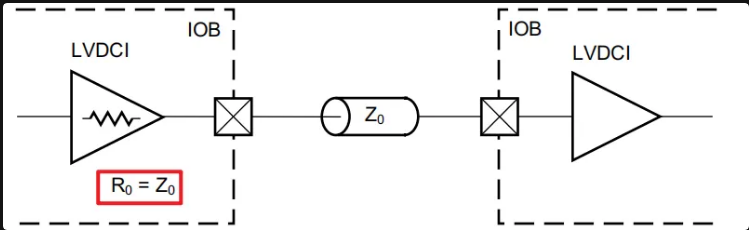

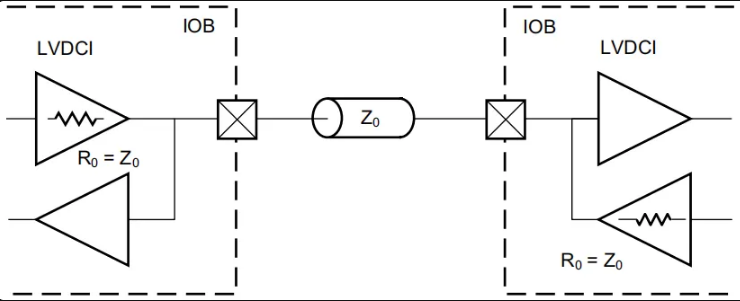

如下图所示,Xilinx支持单向和双向的LVDCI标准,支持1.5V和1.8V两种电平。

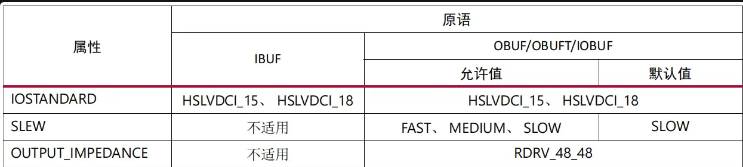

可以使用源终端属性OUTPUT_IMPEDANCE来对匹配电阻进行约束,对于LVDCI标准,只能配置为48Ω,也就是RDRV_48_48。

如下图是支持该标准的原语以及属性配置。

1.2HSLVDCI

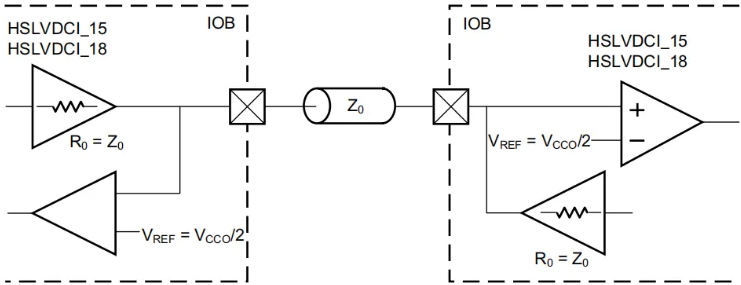

HSLVDCI即High-Speed LVDCI,与LVDCI相比使用HSLVDCI可以具有更高的输入灵敏度,那支持的频率也就更高了。输出端的电气特性与LVDCI相同,输入端与HSTL或SSTL电气特性相同,是采用差分输入BUF的单端I/O(Single-ended I/O standards with a differential input buffer),也就是差分输入的一个端口接输入信号,另一个端口接参考电压VREF,如下图所示,该标准支持1.5V和1.8V。

该标准支持的原语及属性约束如下表所示

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我