1.1 UltraScale系列selectio之IOB的架构

首先得特意强调下本文所说的是7系列Xilinx FPGA的IOB的架构,因为UltraScale系列架构与之有着不小差别。本文会从三个方面来展开:

1、介绍BANK,从整体上了解selectio的组成方式

2、简述HP BANK与HR BANK的区别,

3、阐明IOB的特点,以此进一步的窥探selectio的组成特点

1BANK

xilinx FPGA可以说是以BNAK为单位堆叠起来的,当我们打开实现后的“device”可以看到FPGA的整体结构,整体的下一步细分则是BANK,不同系列不同大小的FPGA的BANK数量和宽度是不一样的,但长度是一样的,均是可以包含50个I/O,但并不是每个bank都会有IOB,这个根据芯片分装来决定的。

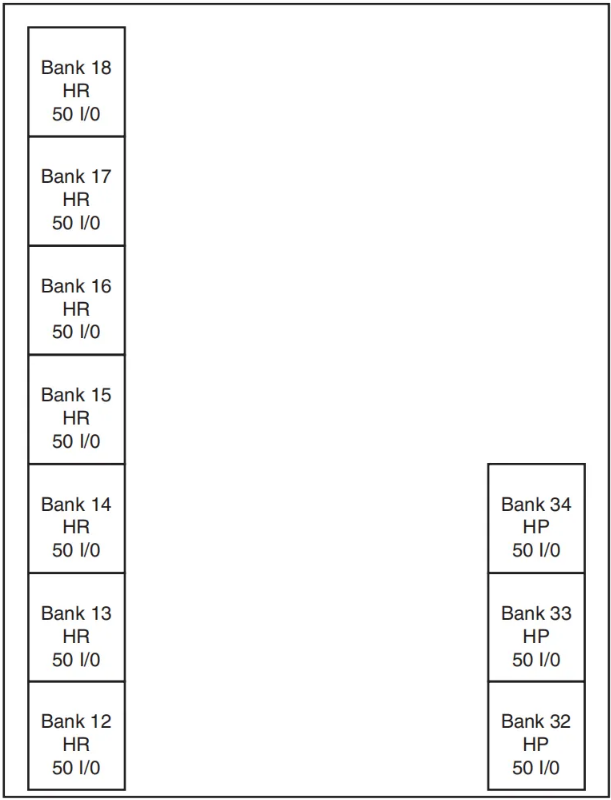

此外,BANK也分为HP BANK和HR BANK,正如下图所示,为XC7K325T的示意图,一共10个BANK,7个HR,3个HP。并不是每个系列FPGA都会有HP,例如A7200T也有10个BANK,但只有9个BANK有IO,且均为HR。

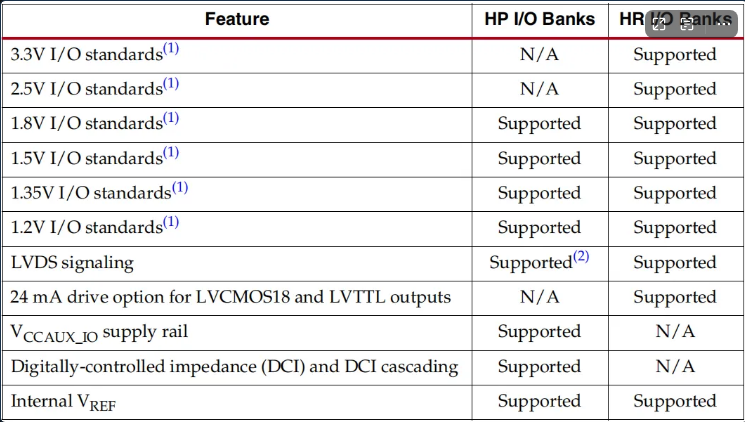

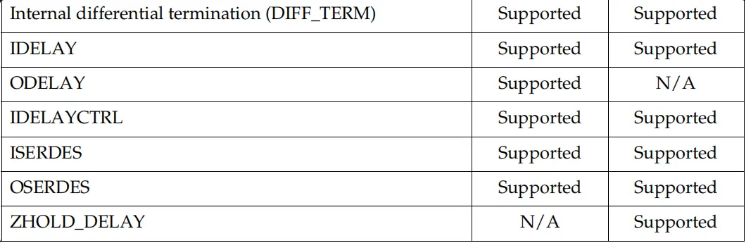

HP(high-performance)即高性能 ,HR(high-range)即高范围。HP旨在满足高速存储器和其他芯片间接口的性能要求,DCI也仅在HP中存在,而HR支持更广泛的I/O标准。虽说HP和HR主要是在性能上的区别,但HR也能支持到非常高的速率。此外HP和HR的区别如下:

总结来说两者区别在于:

1、HP支持能够支持更高的频率

2、HP不支持2.5V和3.3V的,HR支持

3、HP支持VCCAUX_IO和DCI,HR不支持

2I/OB

现在我们知道了每个BANK有50个IO,但这50个IO也不是说一模一样的,部分IO也有其特定的功能

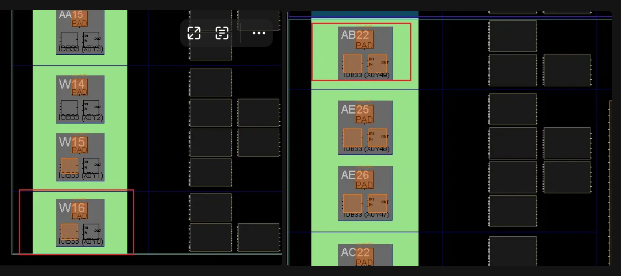

1、有2个IO只能做单端,另外48个可以作为24组差分使用。这两个单端分别位于BANK的两端如下图所示,这50个引脚都能作为单端使用,支持的电压标准也比较多,这个放在后面文章描述。

2、每个BANK都有两个是VREF,可以作为具有差分输入缓冲区的单端I/O的一个输入参考电压(VREF)。

3、每个BANK都有四个MRCC和4个SRCC。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我