1.4 selectio之I/O标准和终端技术(三)

2HSTL

HSTL是high-speed transceiver logic的缩写,是遵照JESD8-6的通用高速总线标准。HSTL有4种变体包括:HSTL class-I、HSTL class-II、Differential HSTL Class I和Differential HSTL Class II。前两者与后两者的区别在于前两个是单端版本,后面是差分版本。从Xilinx提供的文档来看,class-I和class-II的区别在于class-I可以支持1.8V、1.5V和1.2V,class-II仅支持1.8V和1.5V。HR BANK支持class-I中不带DCI的1.8V和1.5V和class-II类型,HP BANK不支持class-II类型,支持class-I的所有类型。

2.1HSTL Class I

该类型是支持单端通信,其中parallel-termination voltage (VTT)电压值因为Vcoo的一半,且等于VREF电压值。

1、HSTL_ I/HSTL_ I_18:HR和HP BANK均支持,支持电压为1.5V/1.8V

2、HSTL_I_12:是支持1.2V的版本,仅HP BANK支持,

3、HSTL_ I_DCI/HSTL_ I_DCI_12/HSTL_ I_DCI_18:带有DCI支持仅HP BANK支持

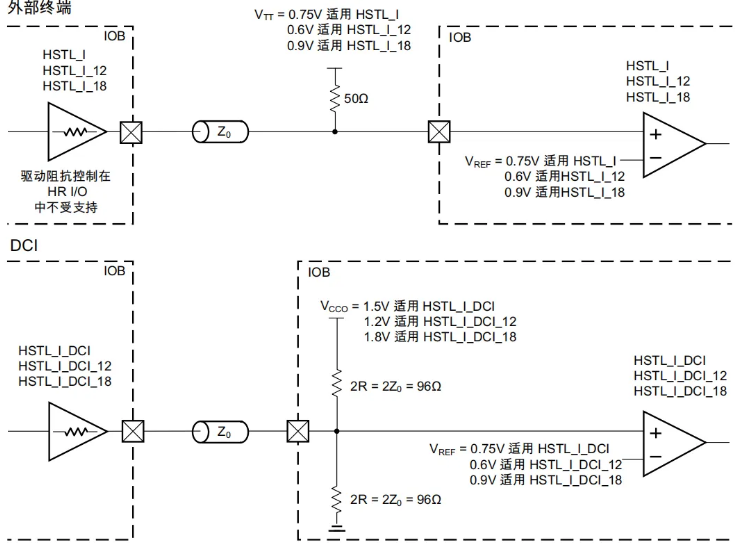

电气结构如下图所示:

1、源端阻抗匹配可通过OUTPUT_IMPEDANCE约束添加非DCI调节的匹配阻抗,支持40Ω、48Ω和60Ω。默认为48Ω,BANK的RVRP需连接240Ω

2、终端如果采用芯片内置终端则是采用戴维南电路,如果采用外部终端匹配则将信号线接到标准电平的二分之一,即采用上拉单端电阻做阻抗匹配。

3、Vref电压需等于标准电平的二分之一,也就是VCCO/2。形成单端输入到差分buf。

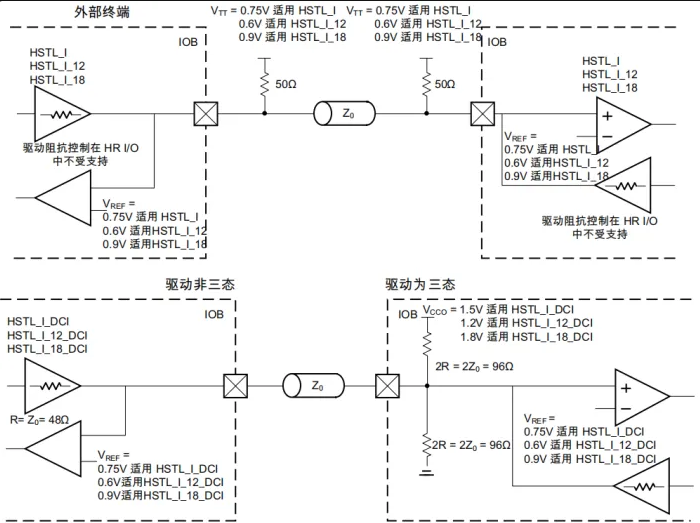

如下图是支持双向通信的实现方案,

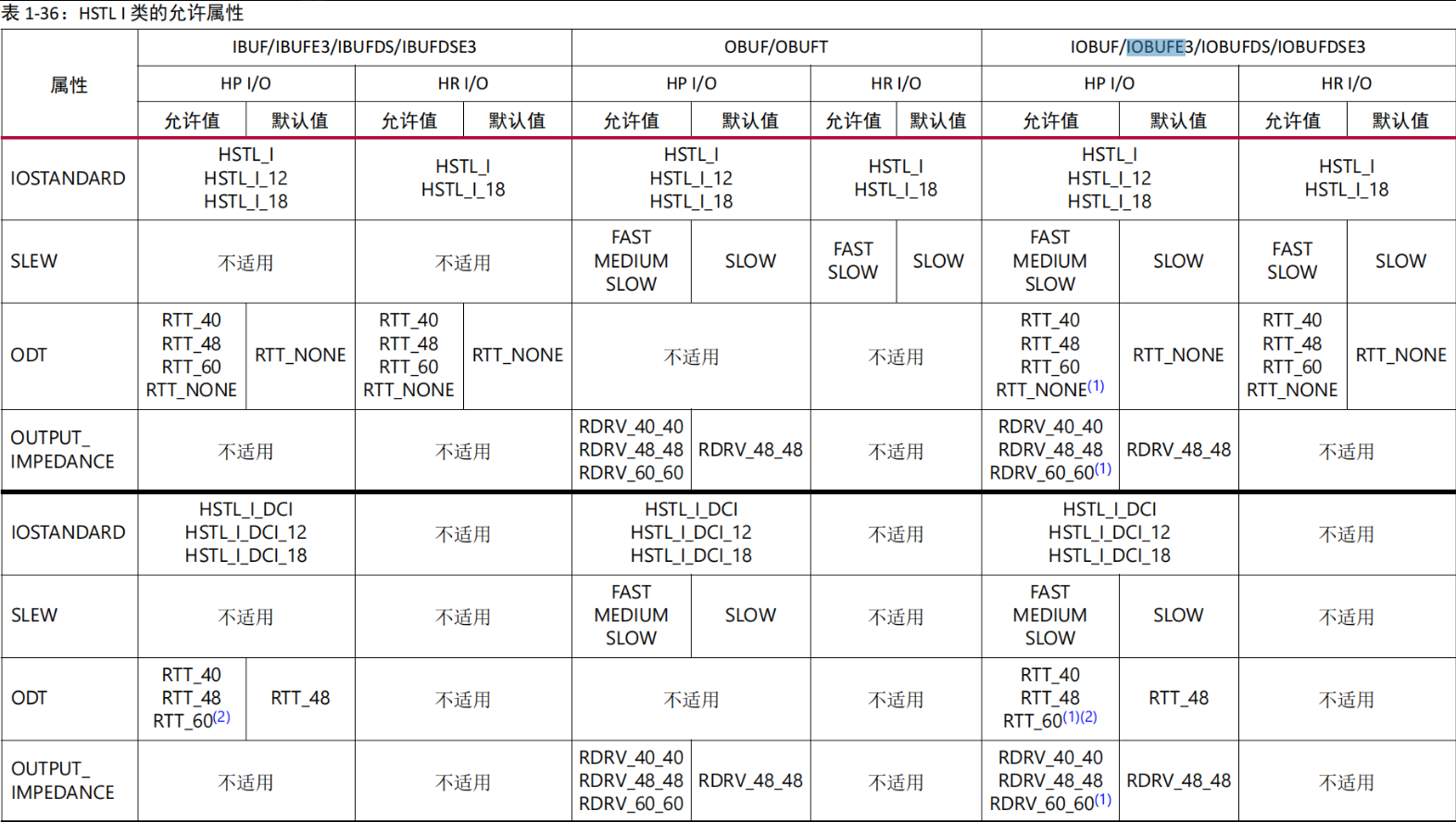

如下图是1类允许的原语及属性约束。

2.2Differential HSTL Class I

该类有六种形式,也可分为支持DCI和不支持DCI两种,这六类均支持单向、双向的差分通信,支持1.2V、1.5V和1.8V,结合Xilinx提供电路有多种方式实现。

1、DIFF_HSTL_I/DIFF_HSTL_I_18/DIFF_HSTL_I_12:HP BANK均支持,HR BANK支持1.8和1.5V

2、DIFF_HSTL_I_DCI/DIFF_HSTL_I_DCI_18/DIFF_HSTL_I_DCI_12:HP BANK支持

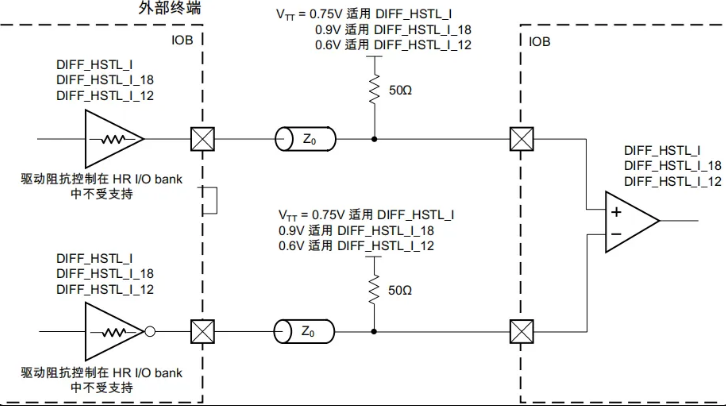

如下图是不带DCI的差分HSTL的一种实现方法,源端接终端电阻,终端外部接单端上拉电阻做阻抗匹配。

如下图是支持双向通信的电路。

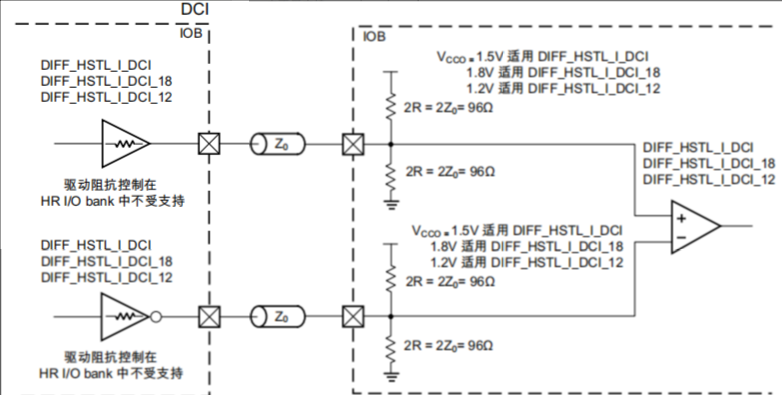

如下是带DCI的电路。

2.3HSTL Class II

该类型包括差分和单端两种形式,均支持1.5V和1.8V,仅HR BANK 支持,电路与Class I差不多。

HSTL_II/HSTL_ II_18,

DIFF_HSTL_II/DIFF_HSTL_II_18

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我