1.4 UltraScale系列selectio之IO的约束原则(下)

内容简介

2024-01-31

11、Internal VREF

这个用于调用每个BANK的内部参考电压并指定参考电压值的大小的。每个BANK都有VREF这样的引脚用来表示这个BANK的参考电压的大小,注意是整个BANK。例如HSTL_II这个I/O标准的接收端是单端输入差分接收,那么差分的N端的值就是这个VREF。

UltraScale系列为VREF参考电压值的产生提供了另外一种方法,也就是内部根据VCOO来产生,约束通过INTERNAL_VREF来实现,约束命令如下:

set_property INTERNAL_VREF value [get_iobanks BANK_number]

value的值可设为0.60、0.675、0.70、0.75、0.84和0.90这几种。

示例 1:使用 HSTL_II (1.5V) 且需要 0.75V 参考电压的 bank 84 的 INTERNAL_VREF 使用以下约束:

set_property INTERNAL_VREF 0.75 [get_iobanks 84]

但注意,使用内部产生的VREF也不能将外部的VERF作为普通IO引脚来使用,因为他是专用引脚。如果使用内部产生的,外部的应通过 500Ω 或 1KΩ 电阻将专用外部 VREF 管脚连接至 GND

12、DQS_BIAS

这个对于一些没有驱动或者说没有使用的差分引脚提供了保持功能。

对于DIFF_SSTL, DIFF_HSUL, and DIFF_POD这些IO标准,会将N端弱拉到VCCO,P端接地

对于LVDS输入,会将P和N均置为VCCO/2

约束命令如下所示:

set_property DQS_BIAS TRUE|FALSE [get_ports port_name]

默认为FALSE,TRUE表示使能该功能,注意不能与PULLTYPE约束同时使用。

13、发送端的预加重

预加重即Pre-Emphasis,对于7系列的FPGA,预加重技术是应用于serdes的,对于UltraScale系列,通用IO引脚也提供了这样的功能,主要是用于类似DDR4这样的高速数据传输的。

预加重的主要目的是提高信号在接收端的可靠性减少失真,信号在链路传输会因阻抗原因出现失真和衰减,也就是高电平可能由1.5V变成了1.3V,原本上升沿挺陡的结果变斜坡了,而且高频的衰减程度要高于低频信号没所以基于此,对高频信号做个预加重,让它衰减后预低频信号差不多,预加重的方法就是抬高跳变沿的幅值,例如原本1.5V,发送时让跳变沿这一小部分区间变为1.7V,这样衰减后还能保持1.5V,当然这只是一个形象的例子。

xilinx用PRE_EMPHASIS描述预加重,XDC的约束如下:

set_property PRE_EMPHASIS value [get_ports port_name]

value值可设为RDRV_NONE或RDRV_240,默认是RDRV_NONE,如果启用预加重,需将 ENABLE_PRE_EMPHASIS设置为TURE。

14、LVDS源端的预加重

英文手册的描述是“LVDS transmitter pre-emphasis”,也就是LVDS发送端的预加重,用LVDS_PRE_EMPHASIS进行约束,如下所示:

set_property LVDS_PRE_EMPHASIS TRUE|FALSE [get_ports port_name]

与PRE_EMPHASIS的区别在于更有针对性,仅应用于LVDS I/O标准的预加重,默认为 FALSE,使用时需设置为TRUE。

需注意,使用预加重时需将ENABLE_PRE_EMPHASIS设置为TRUE,否则不起作用。

15、接收端的均衡器(equalization)

接收端的均衡器(receiver equalization)也就是信号均衡(Signal Equalization),是一种数字通信系统中的信号处理技术。通过对接收信号进行处理,例如线性均衡器、决定性序列估计(DFE)、自适应均衡器等以补偿信号在传输过程中受到的失真和干扰,以提高接收信号的质量和可靠性。

对于我们应用者来说,需要做的就是在需要的时候给均衡器设置合适的值。由EQUALIZATION属性来决定,约束如下

set_property EQUALIZATION value [get_ports port_name]

对于HP BANK,允许值如下:

• EQ_LEVEL0

• EQ_LEVEL1

• EQ_LEVEL2

• EQ_LEVEL3

• EQ_LEVEL4

• EQ_NONE (默认值)

对于HR BANK,允许值如下:

• EQ_LEVEL0

• EQ_LEVEL0_DC_BIAS

• EQ_LEVEL1

• EQ_LEVEL1_DC_BIAS

• EQ_LEVEL2

• EQ_LEVEL2_DC_BIAS

• EQ_LEVEL3

• EQ_LEVEL3_DC_BIAS

• EQ_LEVEL4

• EQ_LEVEL4_DC_BIAS

• EQ_NONE (默认值)

需注意,使用均衡器的端口不能使用PULLTYPE属性进行约束。

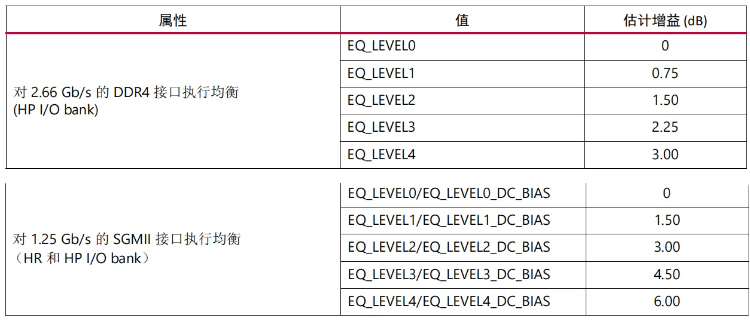

在 DDR4 和 SGMII 接口中采用不同 Equalization 值的典型 AC 增益如下:

16、接收端的偏移控制

接收器偏移控制 (OFFSET_CNTRL) 功能允许针对某些 I/O 标准在接收器中对信号进行偏移,以补偿由于工艺引起的偏移变化。

OFFSET_CNTRL 属性的有效值为:

• CNTRL_NONE (默认值)

• FABRIC

OFFSET_CNTRL 属性在 XDC 文件中使用以下语法:

set_property OFFSET_CNTRL value [get_ports port_name]

要在I/O bank中调用偏移消除功能,必须将 OFFSET_CNTRL设置为FABRIC。可以使用 IBUFE3、IBUFDSE3、IOBUFE3或 IOBUFDSE3原语来使用偏移消除控制功能。

17、VREF_CNTR

VREF_CNTR是用于描述HP bank中接收端VREF扫描功能属性的。它与 HPIO_VREF UNISIM 原语一起使用。 VREF_CNTR 属性的有效值为:

• FABRIC_RANGE1 (POD 标准)

• FABRIC_RANGE2 (其它适用标准)

调用接收器 VREF 扫描功能时, FABRIC_RANGE1 与 POD 标准一起使用,而 FABRIC_RANGE2 与其它适用标准一起使用。

18、DATA_RATE

DATA_RATE 是仅供参考的属性,用于 Vivado Design Suite 的功耗和时序分析和 SSN 工具使用。此属性为这些工具 提供有关的 I/O速率相关信息。

此属性的有效值为:

• 单倍数据速率 (SDR)

• 双倍数据速率 (DDR)

在非原生 PHY 应用中,此属性的默认值为 SDR。在原生模式应用中 (如果 I/O 连接到原生 PHY 原语之一,例如 IDDRE1、 ODDRE1、 RX_BITSLICE、 TX_BITSLICE 等),则默认值为 DDR,约束为如下。

set_property DATA_RATE SDR|DDR [get_ports port_name]

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我