1.3 UltraScale系列selectio之IO的约束原则(上)

这是介绍Xilinx官方手册的第6篇文章

内容简介

2024-01-31

1、DCI_CASCADE约束

这是关于DCI的级联约束,Xilinx允许同列多BANK级联共享VRP/VRN,下面这条约束就是确定主BANK和从BANK的,具体如何实现级联可参考相关文章。

set_property DCI_CASCADE {slave_banks} [get_iobanks master_bank]

2、位置约束

位置约束也就是确定外设与FPGA进行数据交互的引脚,可以使用PACKAGE_PIN来进行约束,使用方式为如下。

set_property PACKAGE_PIN pin_name [get_ports port_name]

“pin_name”是xilinx对芯片引脚定义的名字。“port_name”是我们对该引脚应用起的名字。例如我们用P22引脚来连接led灯,则约束可描述为:

set_property PACKAGE_PIN P22 [get_ports led]

3、I/O标准

有了引脚的位置约束,还需要做的是I/O标准的约束,也就是表示这个引脚承载的电信号的特性,包括了电平大小和电路连接关系等等,通过如下的IOSTANDARD约束可实现。

set_property IOSTANDARD value [get_ports port_name]

具体约束因与外设电路对应,例如电灯和lvds通讯的不可能用相同的电平标准,高速串行通讯也不可能与低速串行通讯用一个标准,唯有指定了I/O标准,软件才能对芯片做正确的配置。

xilinx支持的I/O标准即XXX文章中所表示内容。其中“value”是我们约束的I标准,xilinx支持的范围非常广泛有70多种,例如我们熟悉的LVTTL、LVCMOS18,也有应用比较少的HSTL_I_DCI_12,当然并不是所有的芯片所有引脚都支持这么多种电平标准,例如HR和HP的bank是有区别的,A7和K7也是有区别的,但对于FPGA逻辑设计者来说,这到不用太过考虑用什么,硬件工程师早已在硬件设计时绑定好了,我们只需了解和正确的约束。“port_name”是我们对该引脚应用起的名字。例如我把绑定到led灯的引脚电平约束为LVTTL,则可描述为:

set_property IOSTANDARD LVTTL [get_ports led]

4、IBUF_LOW_PWR 属性

这是一个与功耗相关的约束,如果设为“TURE”使能该属性,则表示对应IO在低功耗下运行,如果不使能,则是在高功耗下运行,而低功耗和高功耗的带来的差别体现在性能上,性能的变化反应在通过I/O BUF的延迟上,使用方式如下:

set_property IBUF_LOW_PWR TRUE|FALSE [get_ports port_name]

例如对led灯对应引脚使能高性能

set_property IBUF_LOW_PWR FALSE [get_ports led]

当然,这仅是一个例子,实际这样做事没有必要的,对于led秒级的电平编号,buf带来的延时可以忽略不计,也因此xilinx建议预期以 ≥1600 Mb/s 的数据速率运行的接收器,此属性应设置为 FALSE。

另外我们也可以通过XPE来分析关闭前后的功耗变化,也可以从静态时序报告中看出使能前后的区别。该属性主要应用于LVDS、HSTL等高速电平标准,对于LVTTL设置是无效的。

5、输出斜率

“SLEW”该属性描述的是对于输出BUF提供可选的斜率,支持LVCMOS、LVTTL, SSTL、HSTL、MOBILE_DDR、HSUL和lvds的输出buf。对于HR的斜率的设定有“SLOW”和“FAST”两种情况,HP多加了“MEDIUM”设定,但默认都是“SLOW”,约束格式为:

set_property SLEW value [get_ports port_name]

这有助于在非关键信号切换是最大程度江都电源总线瞬变的默认值。对于高性能应用,例如DDR这种,需指定斜率为FAST,但如果硬件电路设计不当,例如终端、传输线路阻抗连续性和交叉耦合设计不当,则更快的斜率也会导致反射或噪声问题。所以,一般来讲默认即可。

6、输出驱动强度

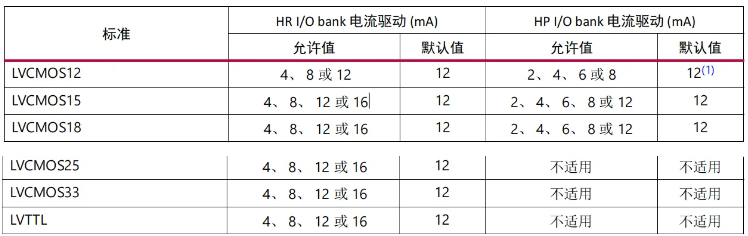

对于 LVCMOS 和 LVTTL 输出缓存,可以使用 DRIVE 属性指定驱动能够安全地驱动到有效逻辑电平(以 mA 为单位)的负载。默认为12mA。

约束为:

set_property DRIVE drive_value [get_ports port_name]

7、PULLTYPE属性

xilinx对IO内置了上拉、下拉电阻,可针对输入BUF、输出BUF及双向BUF实现弱上拉、弱下拉和保持功能。其约束如下所示:

set_property PULLTYPE value [get_ports port_name]

value的值可选为如下四种之一:

• NONE

• PULLUP

• PULLDOWN

• KEEPER

8、片上终端 (ODT) 属性

ODT是On-Die Termination的缩写,译为片上终端,也就是集成在IOB上的终端电阻。与片上终端对应的则是焊在PCB上的终端电阻,这会产生电阻到引脚的短截线影响信号的完整性,片上终端则完全没有这方面的顾虑,所以片上终端可以更好的提高信号的完整性。

一般高频信号需要加终端电阻来减少反射波和干扰原信号,对于低频信号则不需要,在HSTL、 SSTL、 POD 和 HSUL 标准的输入上支持戴维南终端电阻或单端上拉终端电阻。I/O bank 的 VCCO 必须连接到对应I/O标准指定电压上,ODT 属性才能按预期执行,其约束如下图所示:

set_property ODT value [get_ports port_name]

value值可选为如下值,具体选择需根据I/O标准的支持情况以及设计电路的需求。其中RTT_40表示40Ω电阻。

• RTT_40

• RTT_48

• RTT_60

• RTT_120

• RTT_240

• RTT_NONE

9、源端接属性 (OUTPUT_IMPEDANCE)

源短接即Source Termination,表示在信号的发起端添加的端接电阻,用于与信号线的特性阻抗匹配。

UltraScale系列FPGA用OUTPUT_IMPEDANCE来对此进行约束,约束命令如下所示:

set_property OUTPUT_IMPEDANCE value [get_ports port_name]

value可设置值如下,数字表示对应的欧姆值。

• RDRV_40_40

• RDRV_48_48

• RDRV_60_60

• RDRV_NONE_NONE

OUTPUT_IMPEDANCE一版支持的I/O标准有 HSTL、SSTL、 HSUL、LVDCI、 HSLVDCI 和 POD ,并支持带有DCI和不带有DCI的两种标准。具体值得选择需根据I/O标准得允许设置范围及实际电路来决定。

10、差分端接属性

差分端接也就是Differential Termination,针对差分信号内置了100Ω的差分端接电阻,可以在片内进行终端匹配,避免了PCB上挂电阻的麻烦,也避免了因电阻到引脚的短截线所引发的问题。此外,与DCI相比功耗更低,且不用VRP引脚外接电阻做参考。

对于HP BANK,VCCO必须接到1.8V,HR BANK的VCCO必须接到2.5V。且仅可应用于终端,不能用于源端。约束命令有两个即DIFF_TERM和DIFF_TERM_ADV,其中 DIFF_TERM_ADV可用于XDC文件的约束命令, DIFF_TERM是在调用原语是可配置的选项。这两个只需要用一个即可,应该是或的关系。约束命令如下所示:

set_property DIFF_TERM_ADV value [get_ports port_name]

value值可为TERM_NONE或TERM_100,也就是是否使能端接电阻,默认是不使能的。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我