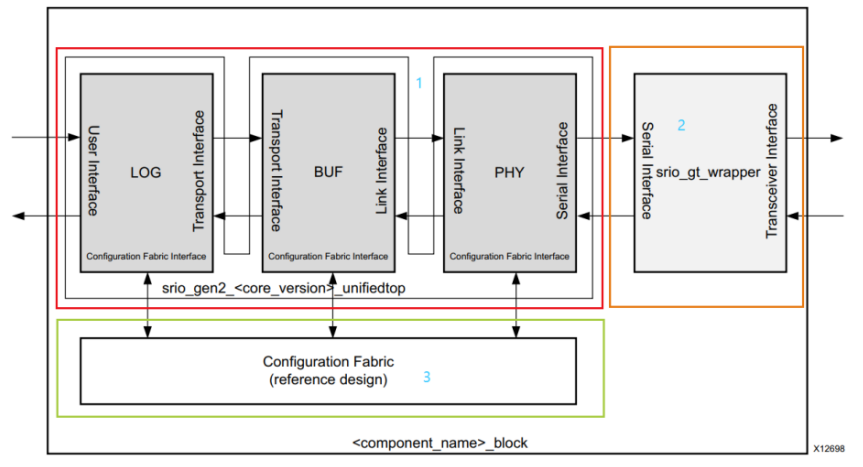

SRIO核的结构剖析-----Buffer接口(BUF)

BUF对于保证包传递和流控制操作是必需的。Xilinx提供了一种可配置的缓冲区解决方案,可以在系统性能和资源需求之间进行权衡。发送缓冲区负责对传出事务进行排队,并管理这些数据包在链路接口上进入PHY的流程。通过Vivado IDE可以将TX和RX缓冲区的大小配置为深度为8、16或32个数据包的值。TX缓冲区是一种存储转发缓冲区,旨在降低数据包到数据包的延迟,以最大程度地提高流吞吐量。传输缓冲区必须保存每个数据包,直到链接伙伴设备已成功接收它为止,此时释放该数据包以为其他数据包腾出空间。 如果缓冲区中积累了多个未发送的数据包(通常在发生流控制时发生),则BUF会根据类型和优先级对数据包进行重新排序,首先发出响应数据包,然后发出请求。

接收缓冲区充当FIFO,用于将数据存储和转发到LOG接收路径。接收缓冲器还具有域交叉逻辑,该逻辑允许逻辑层/用户设计和PHY以不同的时钟速率运行。 与发送缓冲区设计一样,建议将此逻辑用于多通道内核,关于缓冲和流控的具体内容会在下面章节介绍。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我