8、详解面试的必答题——I2C协议 (上)

内容简介

2024-02-02

对于从事FPGA行业的应届生来说,在面试过程中很可能会被问到关于I2C协议的一些内容,尤其是碰到比较重视基本功的面试官,答好了,就是大大的加法,答不上了,也是大大的减分。为什么呢?首先因为这个协议简单,简单的都不会必然容易引起人的遐想,其次,它很好的考查了应试者对时序对协议的理解,FPGA玩的就是时序,如果答不上了那就有理由怀疑FPGA学的程度了。故在此笔者将详细的阐述IIC协议,并用AT24C04芯片进行实验。

”

I2C电路设计的原由

1.1 I2C的发展历史

I2C总线由Philips公司开发的一种简单的双向二线制同步串行总线,英文名称为(Internal-Integrated Circuit Bus),也就是内置集成电路总线,它只需要两根线即可实现系统内部各个连接于总线上的集成电路(IC)之间的信息传递,可以说它是内部的公共通信干线。该协议起初是飞利浦为公司为了让主板、嵌入式系统用以连接低速周边装置而研发的,如今得到了广泛应用。在平时,我们习惯把bus给省略了,称之为I2C或者IIC。

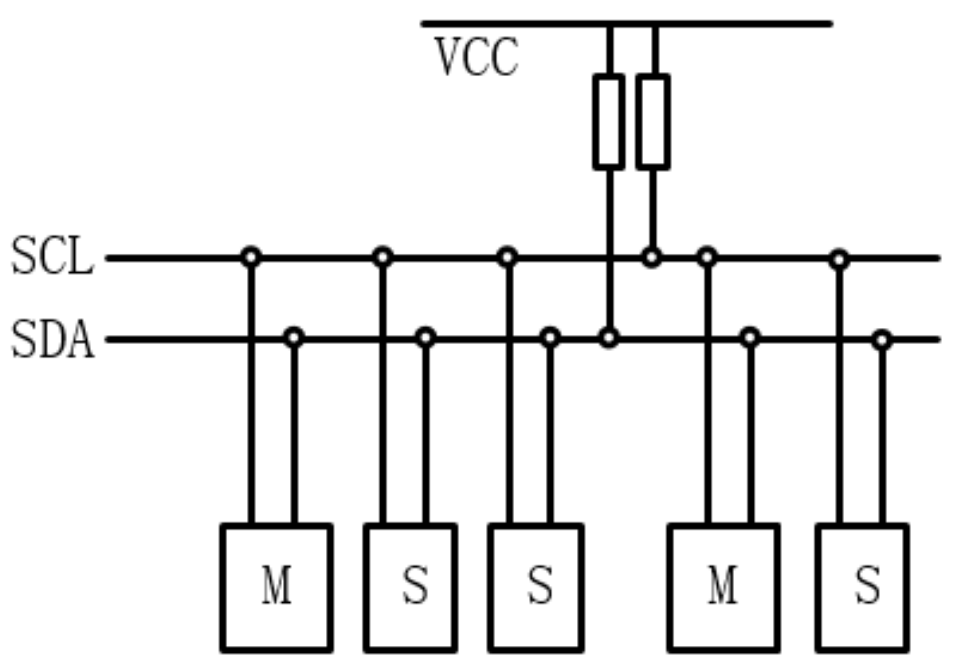

I2C总线设计可为非常精巧,它用两根线就可以实现总线上主从设备之间的交流,并且支持分时复用多主多从,也就是说在同一时刻仅支持一主一从,如图1所示。由于在芯片内部都有I2C相关的电路设计以兼容I2C接口,且片上的滤波器可以滤去总线数据线上的毛刺波保证数据完整,故外部只需要加个上拉电阻即可。

1.2 为什么要加上拉电阻

那么为啥需要上拉电阻呢?因为飞利浦的I2C总线规范要求总线空闲时两根线都必须为高,所以咱就得给人家加上。当然,其原因也是很好理解的。通过I2C进行数据通信说白了就是检测这两根线上的状态,即电平高低,试想,如果空闲是不定态或者说为低电平,那就无法实现这一需求了,毕竟谁也不能把低电平拉高。

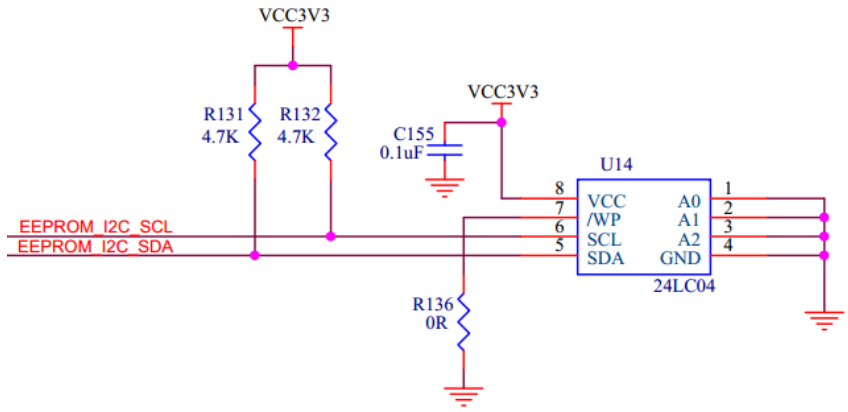

这个上拉电阻也是有讲究的,不是说随便怼上一个就Ok了。总的来说电源电压限制了上拉电阻的最小值,负载电容(总线电容)限制了上拉电阻的最大值。如果上拉电阻值过小,灌入端口的电流会变大,这样会导致MOS管由饱和状态变成放大状态,这样端口输出的低电平值增大,I2C协议规定,端口输出低电平的最高允许值为0.4V,故电阻不能太小。当然,上拉电阻太大致使负载电流太小也不成,但这个影响不及总线电容影响大,故可忽略。上拉电阻会和总线形容RC电路,这就会延长充电时间使得时钟沿更缓,由此影响建立时间进而限制了时钟速率。所以,I2C的上拉电阻可以一般选择1.5K、2.2K或4.7K,如图2所示。

由于I2C总线器件均为CMOS器件,CMOS器件的最大优点就是省电,耗电量极低,一般在微安级,所以I2C总线上基本不会出现电流驱动能力不足的问题,如果出现那设计者也忒抠了吧,这点电都不给。但I2C总线上的IC个数是有限制的,这个限制虽不受制于电流驱动能力,但受制于电容负载总量。

1.3 电容负载的概念

我们先说一下这个“电容负载总量”,也就是总线电容。总线电容即线路连接和管脚的总电容,或者可以理解为集成电路设计和走线中所不可避免产生的寄生电容。由于集成电路的特性使得协议需满足一定的时序要求,也就是建立时间和保持时间,总线电容具有电压滞后电流的特性,也就是会让时钟沿变缓,故为满足时序要求,对总线电容有了限制。所以这个限制是跟频率有关系的,在《I2C总线规范》我们可查阅到,I2C的串行8位双向数据传输位速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s。标准模式最大总线电容为400pF,快速模式最大总线电容为20pF,如果你跑几十bit/s,便可忽略这些限制。

快来扫描下方二维码关注公众号,领取站内所有相关资料,所有哦~

有建议、有需求、有疑问、联系我